Explainer: L1 vs L2 vs L3 Cache

Hver ENESTE CPU som finnes i hvilken som helst datamaskin, fra en billig bærbar pc til en million dollar server, vil ha noe som kalles cache. Mer sannsynlig enn ikke, det vil også ha flere nivåer av det.

det må være viktig, ellers hvorfor skulle det være der? Men hva gjør cache gjøre, og hvorfor behovet for ulike nivåer av ting? Hva i All Verden betyr 12-veis sett assosiativ selv?

hva er egentlig cache?

TL;DR: det er lite, MEN veldig raskt minne som sitter rett ved SIDEN av CPU-logikkenhetene.

Men selvfølgelig er det mye mer vi kan lære om cache…La oss begynne med et imaginært, magisk lagringssystem: det er uendelig raskt, kan håndtere et uendelig antall datatransaksjoner samtidig, og holder alltid data trygt og sikkert. Ikke at noe selv eksternt til dette eksisterer, men hvis det gjorde det, ville prosessordesign være mye enklere.

Cpuer trenger bare å ha logiske enheter for å legge til, multiplisere osv. og et system for å håndtere dataoverføringer. Dette er fordi vår teoretiske lagringssystem kan umiddelbart sende og motta alle tallene som kreves; ingen av logikkenhetene ville bli holdt opp og vente på en datatransaksjon.

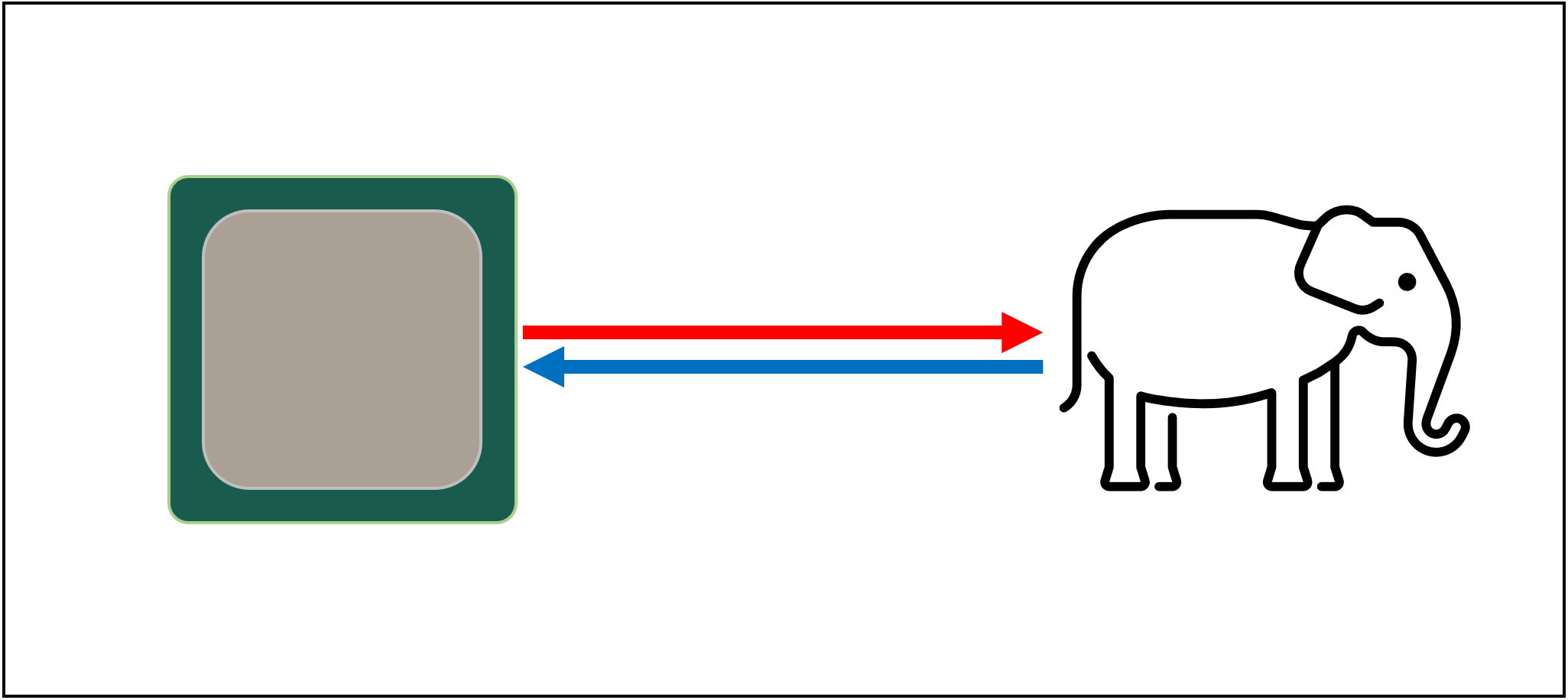

Men som vi alle vet, er det ingen magisk lagringsteknologi. I stedet har vi hard-eller solid state-stasjoner, og selv de beste av disse er ikke engang i stand til å håndtere alle dataoverføringene som kreves for en typisk CPU.

Den Store T ‘ Phon av datalagring

grunnen til at er at moderne Cpuer er utrolig raske-de tar bare en klokke syklus for å legge til to 64 bit heltallsverdier sammen, og for EN CPU som kjører på 4 GHz, ville dette bare være 0.00000000025 sekunder eller en fjerdedel av et nanosekund.i Mellomtiden tar spinnende harddisker tusenvis av nanosekunder bare for å finne data på platene inni, enn si overføre det, og solid state-stasjoner tar fortsatt titalls eller hundrevis av nanosekunder.Slike stasjoner kan åpenbart ikke bygges inn i prosessorer, så det betyr at det vil være en fysisk adskillelse mellom de to. Dette legger bare mer tid på flytting av data, noe som gjør ting enda verre.

Den Store A ‘ Tuin av datalagring, dessverre

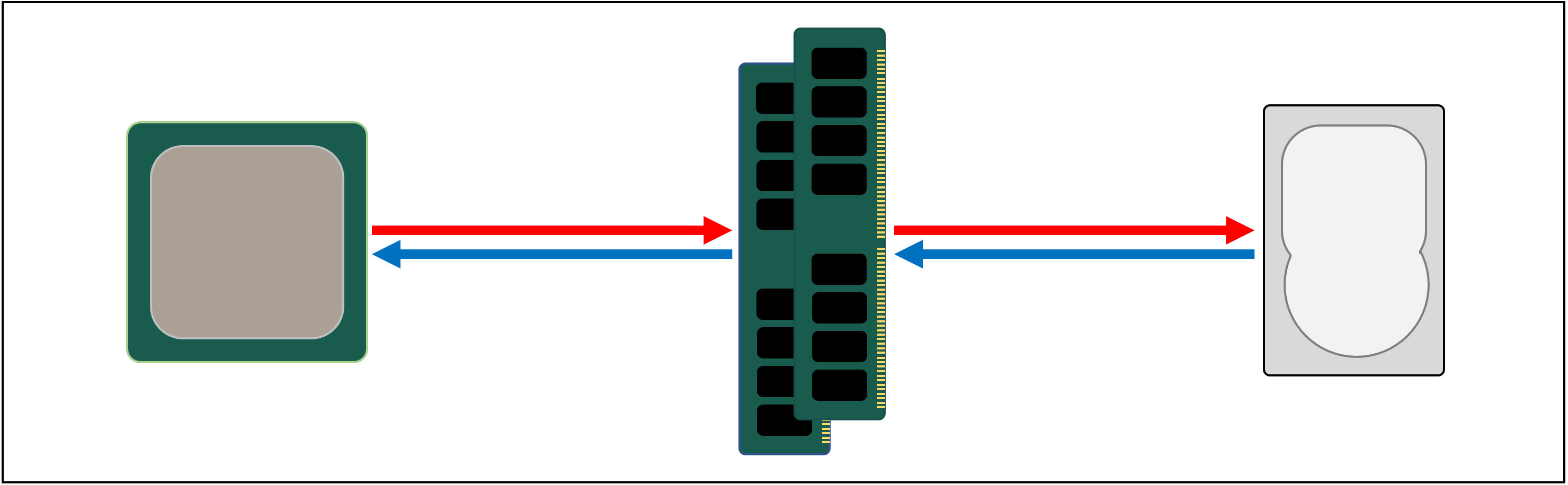

Så det vi trenger er et annet datalagringssystem, som sitter mellom prosessoren og hovedlagringen. Det må være raskere enn en stasjon, kunne håndtere mange dataoverføringer samtidig, og være mye nærmere prosessoren.

Vel, vi har allerede en slik TING, og DET kalles RAM, og hvert datasystem har noe for dette formålet.Nesten av all denne typen lagring er dram (dynamic random access memory), og Det er i stand til å overføre data rundt mye raskere enn noen stasjon.

MEN MENS DRAM er super rask, kan DEN ikke lagre hvor som helst nær så mye data.Noen av De største ddr4-minnebrikkene Laget Av Micron, en Av De få produsentene AV DRAM, har 32 Gbits eller 4 GB data; de største harddiskene holder 4000 ganger mer enn dette.Så selv om vi har forbedret hastigheten på datanettverket vårt, vil det være nødvendig med flere systemer-maskinvare og programvare-for å finne ut hvilke data som skal holdes i den begrensede MENGDEN DRAM, klar for CPU.

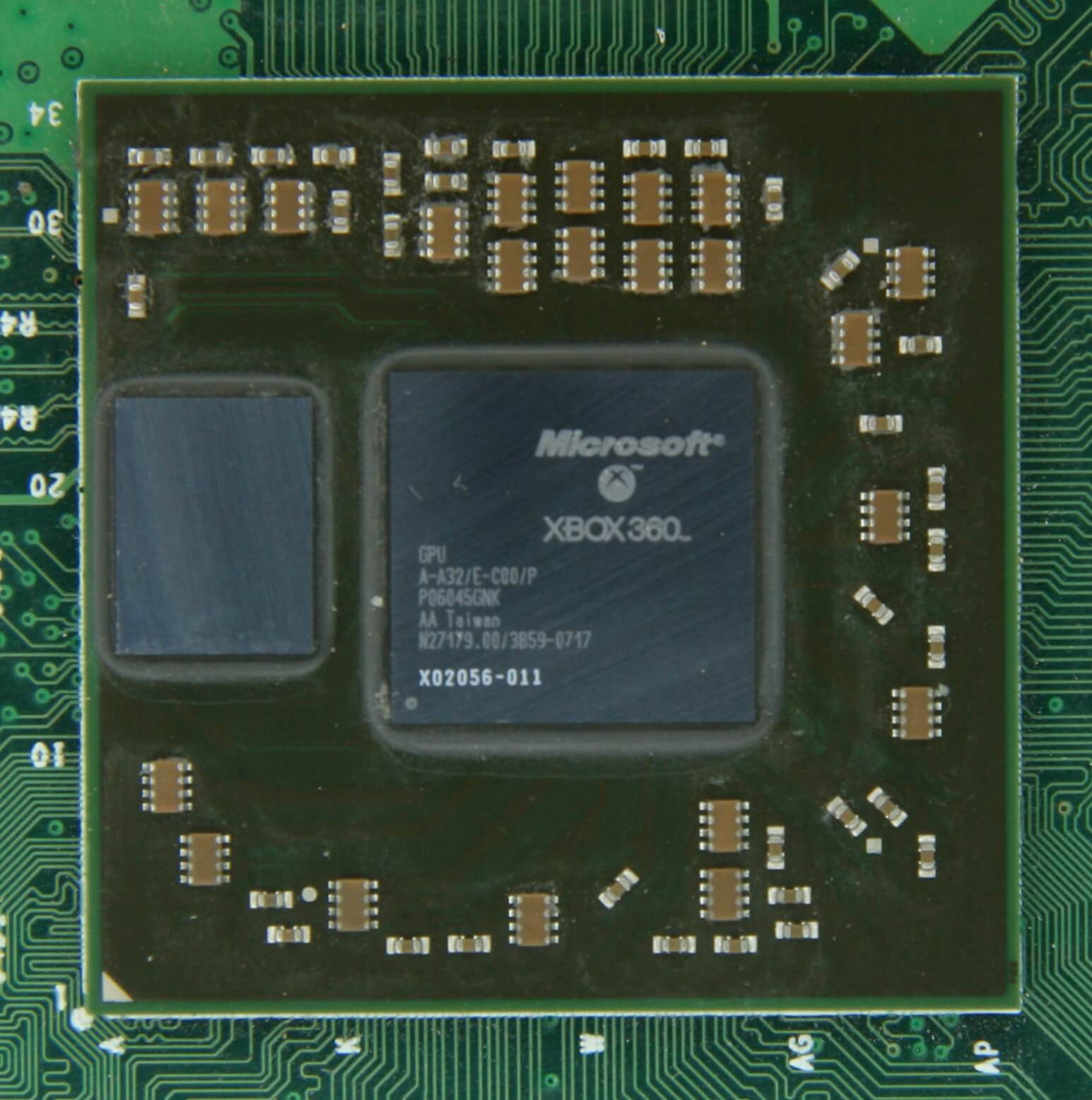

MINST DRAM kan produseres for å være i chip-pakken (kjent som embedded DRAM). Cpuer er ganske små, skjønt, så du kan ikke holde så mye inn i dem.

10 MB DRAM til venstre for Grafikkprosessoren På Xbox 360. DET store flertallet AV DRAM ligger rett ved siden av prosessoren, koblet til hovedkortet, og det er alltid den nærmeste komponenten TIL CPU, i et datasystem. Og likevel er det fortsatt ikke raskt nok…DRAM tar fortsatt rundt 100 nanosekunder for å finne data, men I det minste kan det overføre milliarder biter hvert sekund. Ser ut til at vi trenger et annet minne, for å gå inn mellom prosessorens enheter og DRAM.

Skriv inn trinn til venstre: SRAM (statisk random access memory). HVOR DRAM bruker mikroskopiske kondensatorer til å lagre data i form av elektrisk ladning, bruker sram transistorer til å gjøre det samme, og disse kan fungere nesten like fort som logikkenhetene i en prosessor (omtrent 10 ganger raskere enn DRAM).

Det er selvfølgelig en ulempe FOR SRAM, og igjen handler det om plass.Transistor – basert minne tar opp mye mer plass enn DRAM: for samme STØRRELSE 4 GB DDR4 chip, vil DU få mindre ENN 100 MB verdt AV SRAM. MEN siden DET er laget gjennom samme prosess som å lage EN CPU, KAN SRAM bygges rett inne i prosessoren, så nær logikkenhetene som mulig.Transistor – basert minne tar opp mye mer plass enn DRAM: for samme STØRRELSE 4 GB DDR4 chip, vil DU få mindre ENN 100 MB verdt AV SRAM.

med hvert ekstra trinn har vi økt hastigheten på å flytte data om, til kostnaden for hvor mye vi kan lagre. Vi kunne fortsette å legge i flere seksjoner, med hver og en blir raskere, men mindre.og så kommer vi til en mer teknisk definisjon av hva cache er: det er flere blokker AV SRAM, alle plassert inne i prosessoren; de er vant til å sikre at logikkenhetene holdes så opptatt som mulig, ved å sende og lagre data med super raske hastigheter. Fornøyd med det? Bra – fordi det kommer til å bli mye mer komplisert herfra!

Cache: en parkeringsplass på flere nivåer

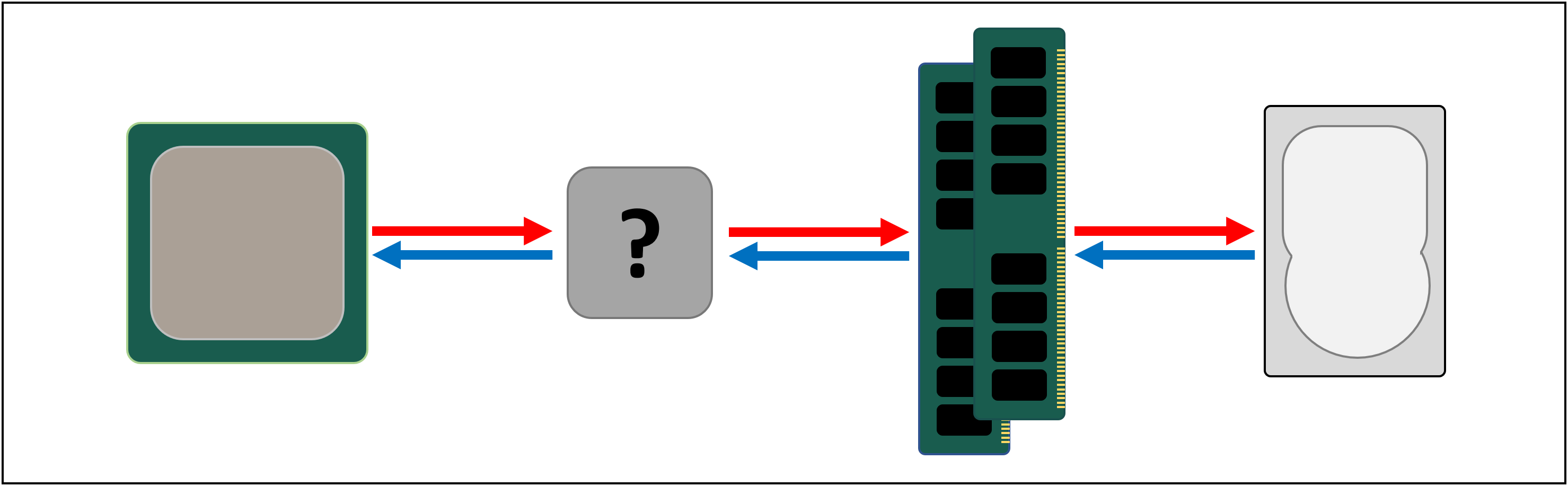

som vi diskuterte, er cache nødvendig fordi det ikke er et magisk lagringssystem som kan holde tritt med datakravene til logikkenhetene i en prosessor. Moderne Prosessorer og grafikkprosessorer inneholder et antall sram-blokker, som er internt organisert i et hierarki-en sekvens av cacher som er ordnet som følger:

I bildet ovenfor er CPUEN representert av det svarte stiplede rektangelet. ALUs (aritmetiske logiske enheter) er helt til venstre; dette er strukturene som driver prosessoren, håndterer matematikken brikken gjør. Selv om det ikke er teknisk cache, er det nærmeste minnenivået Til Alu-ene registre (de er gruppert sammen i en registerfil).

Hver av disse har et enkelt tall, for eksempel et 64-biters heltall; verdien i seg selv kan være et stykke data om noe, en kode for en bestemt instruksjon eller minneadressen til noen andre data.registerfilen i en stasjonær CPU er ganske liten-for Eksempel I Intels Core i9-9900K er det to banker av dem i hver kjerne, og den for heltall inneholder bare 180 64-bits registre. Den andre registerfilen, for vektorer (små arrays av tall), har 168 256-biters oppføringer. Så den totale registerfilen for hver kjerne er litt under 7 kB. Til sammenligning er registerfilen i Streaming Multiprocessors (GPUS ekvivalent MED EN CPU-kjerne) Av En Nvidia GeForce RTX 2080 Ti 256 kB i størrelse.

Registre er SRAM, akkurat som cache, men de er like raske som Aluene de tjener, og skyver data inn og ut i en enkelt klokke syklus. Men de er ikke laget for å holde veldig mye data (bare et enkelt stykke av det), og derfor er det alltid noen større blokker med minne i nærheten: dette er Nivå 1-cachen.

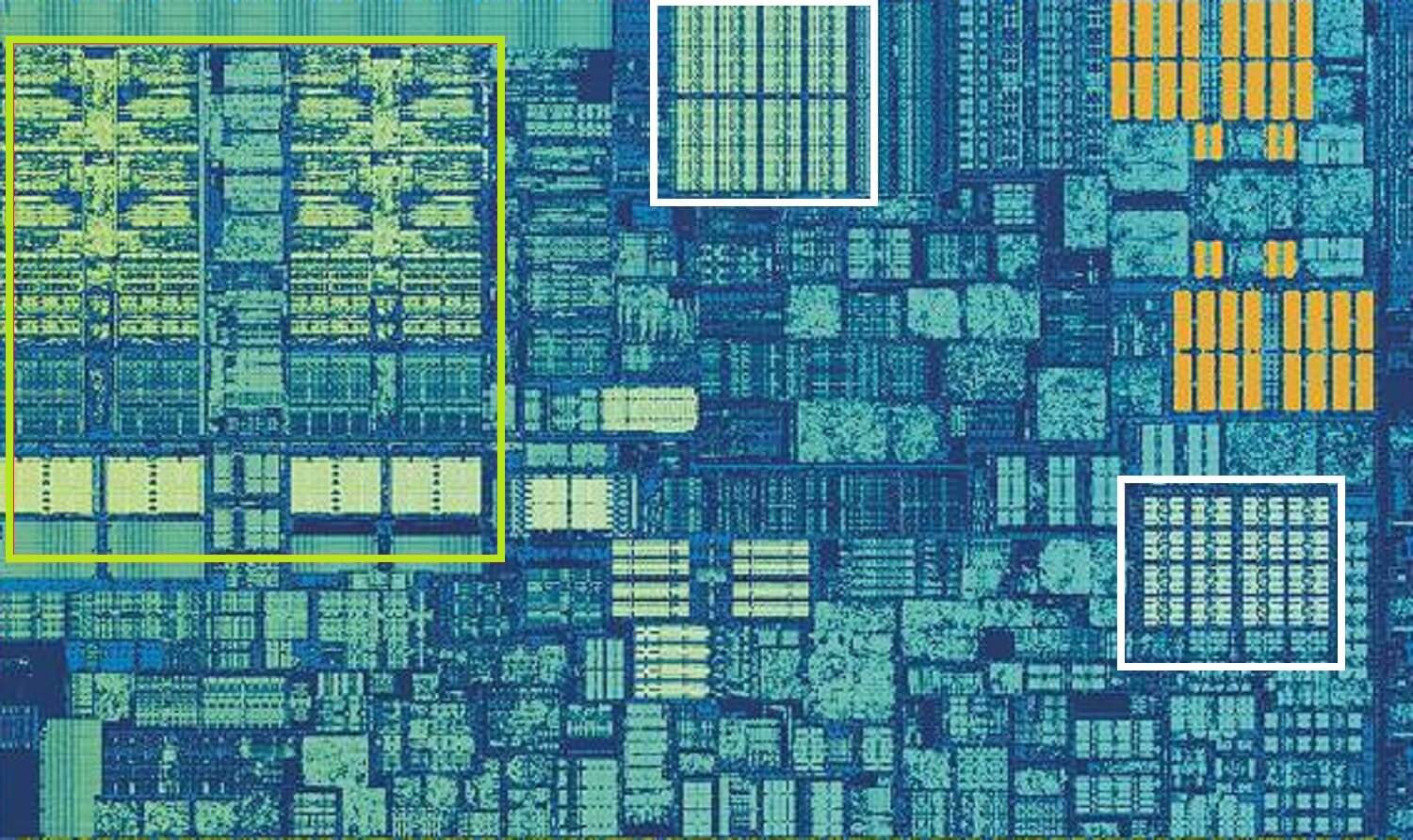

Intel Skylake CPU, zoomet inn skudd av en enkelt kjerne. Kilde: Wikichip

bildet ovenfor er et zoomet inn skudd av En enkelt kjerne fra Intels Skylake desktop processor design.

Aluene og registerfilene kan ses helt til venstre, uthevet i grønt. I toppen-midten av bildet, i hvitt, Er nivå 1 data cache. Dette holder ikke mye informasjon, bare 32 kB, men som registre er det svært nær logikkenhetene og kjører i samme hastighet som dem.

det andre hvite rektangelet angir Nivå 1 Instruksjonsbuffer, også 32 kB i størrelse. Som navnet antyder, lagrer Dette ulike kommandoer som er klare til å bli delt opp i mindre, såkalte mikrooperasjoner (vanligvis merket som µ), For Aluene å utføre. Det er også en cache for dem, og du kan klassifisere Den som Nivå 0, da den er mindre (bare holder 1500 operasjoner) og nærmere Enn L1-cachene.

du lurer kanskje på hvorfor disse blokkene AV SRAM er så små; hvorfor er de ikke en megabyte i størrelse? Sammen tar data – og instruksjonsbufferne nesten like mye plass i brikken som de viktigste logiske enhetene gjør, slik at de blir større, vil øke den totale størrelsen på dysen.Men hovedårsaken til at de bare holder noen få kB, er at tiden som trengs for å finne og hente data øker etter hvert som minnekapasiteten blir større. L1 cache må være veldig rask, og så et kompromiss må nås, mellom størrelse og hastighet-i beste fall tar det rundt 5 klokkesykluser (lengre for flyttallsverdier) for å få dataene ut av denne hurtigbufferen, klar til bruk.

Skylake ‘ S L2 cache: 256 kB SRAM godhet

Men hvis dette var den eneste cachen inne i en prosessor, ville ytelsen slå en plutselig vegg. Det er derfor de alle har et annet nivå av minne innebygd i kjernene: nivå 2-cachen. Dette er en generell blokk med lagring, holder på instruksjoner og data.DET er alltid litt større Enn Nivå 1: AMD Zen 2-prosessorer pakker opp til 512 kB, slik at de lavere nivåene kan holdes godt forsynt. Denne ekstra størrelsen kommer imidlertid til en pris, og det tar omtrent dobbelt så lang tid å finne og overføre dataene fra denne cachen, sammenlignet Med Nivå 1.

Går tilbake i tid, til dagene til Den opprinnelige Intel Pentium, nivå 2 cache var en egen chip, enten på et lite plug-in kretskort (som EN RAM DIMM) eller innebygd i hovedkortet. Det jobbet til slutt på CPU-pakken selv, til den endelig ble integrert i CPU-dysen, i Slike Som Pentium III OG AMD K6-III-prosessorer.denne utviklingen ble snart etterfulgt av et annet nivå av cache, der for å støtte de andre lavere nivåene, og det kom på grunn av økningen av multi-core chips.

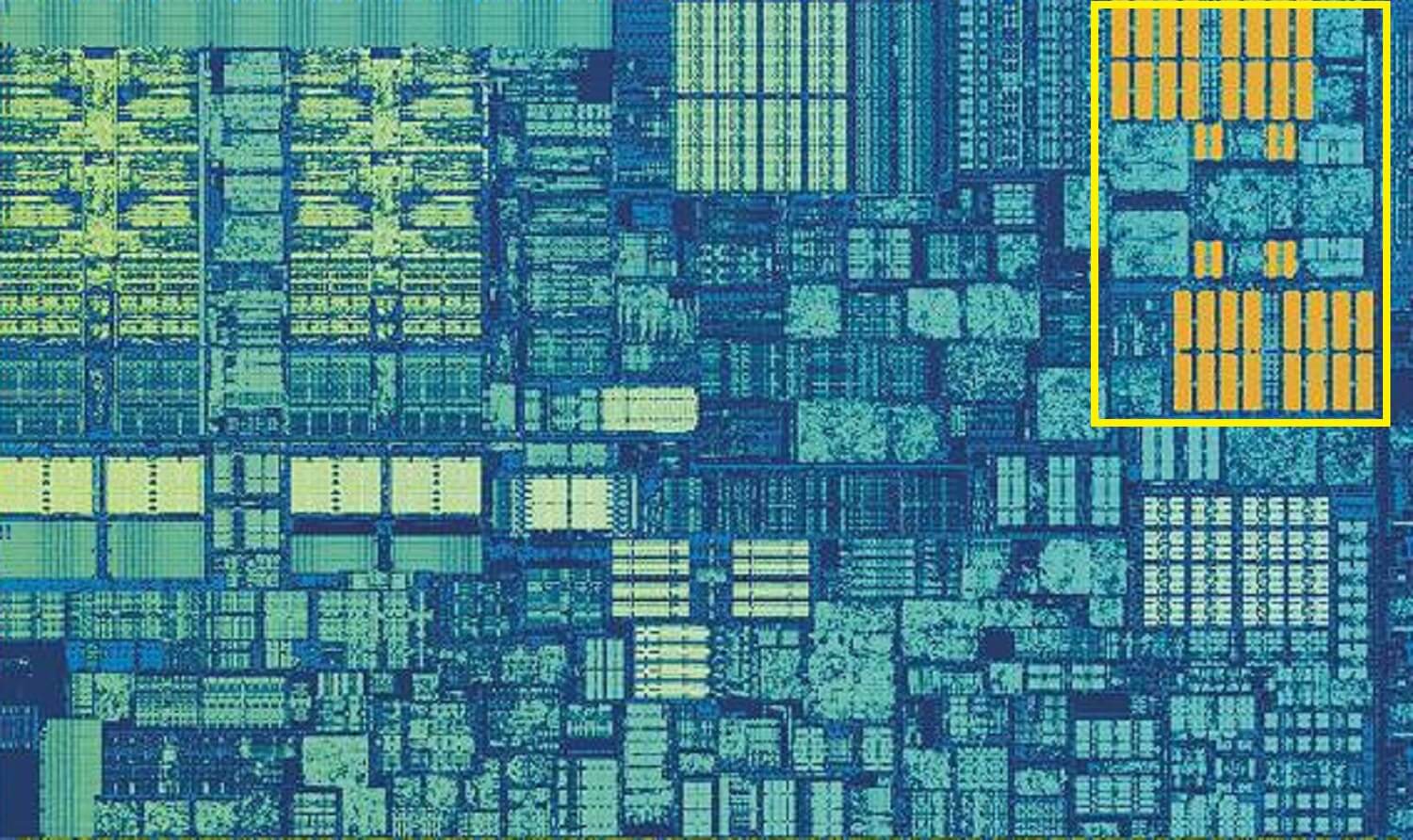

Intel Kaby Lake chip. Kilde: Wikichip

dette bildet, Av En Intel Kaby Lake-chip, viser 4 kjerner i venstre-midten (en integrert GPU tar opp nesten halvparten av terningen, til høyre). Hver kjerne har sitt eget ‘private’ sett Med Nivå 1 og 2 cacher (hvite og gule høydepunkter), men de kommer også med et tredje sett MED SRAM-blokker.nivå 3 cache, selv om det er direkte rundt en enkelt kjerne, er fullt delt med de andre-hver og en kan fritt få tilgang til innholdet i en annens l3 cache. Det er mye større (mellom 2 OG 32 MB), men også mye tregere, gjennomsnittlig over 30 sykluser, spesielt hvis en kjerne trenger å bruke data som er i en blokk med cache litt avstand unna.

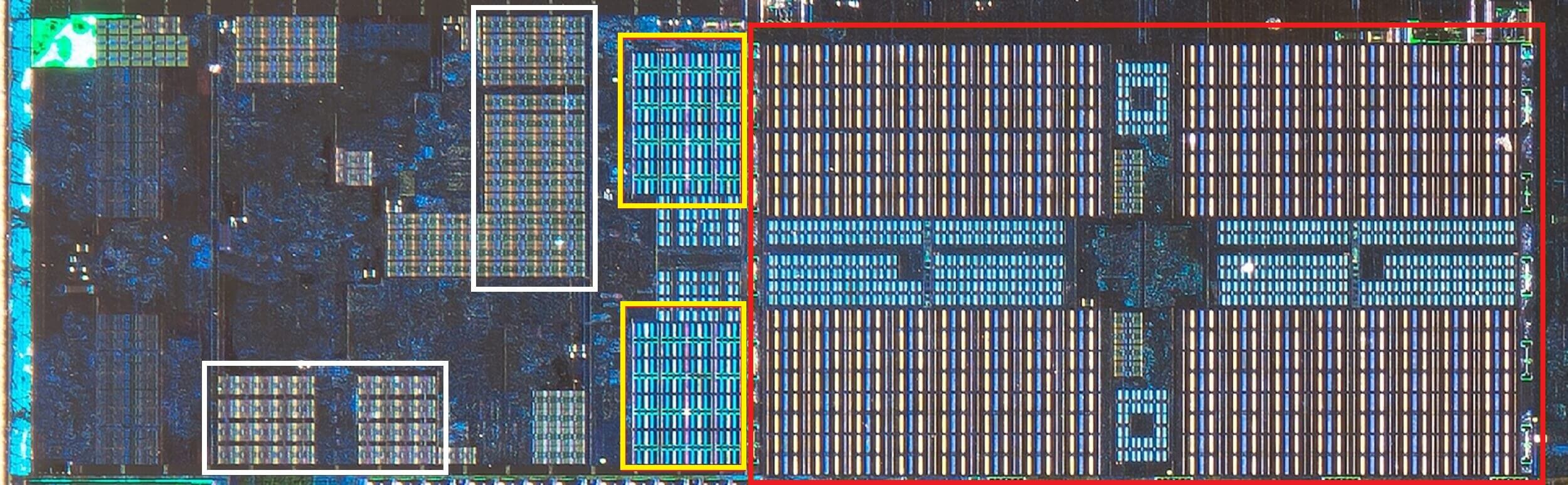

Nedenfor kan vi se en enkelt kjerne I AMDS Zen 2-arkitektur: 32 kB nivå 1 data og instruksjon cacher i hvitt, 512 KB nivå 2 i gul, og en enorm 4 MB blokk Med L3 cache i rødt.

AMD Zen 2 CPU, zoomet inn skudd av en enkelt kjerne. Kilde: Fritzchens Fritz

Vent et sekund. Hvordan kan 32 kB ta opp mer fysisk plass enn 512 kB? Hvis Nivå 1 inneholder så lite data, hvorfor er det proporsjonalt så mye større Enn L2 eller L3 cache?

Mer enn bare et tall

Cache øker ytelsen ved å påskynde dataoverføring til logiske enheter og holde en kopi av ofte brukte instruksjoner og data i nærheten. Informasjonen som er lagret i cache er delt i to deler: selve dataene og plasseringen av hvor den opprinnelig var plassert i systemminne/lagring-denne adressen kalles en cache-tag.

NÅR CPUEN kjører en operasjon som vil lese eller skrive data fra / til minnet, starter den ved å sjekke kodene i Nivå 1-hurtigbufferen. Hvis den nødvendige er til stede (en cache hit), kan dataene da nås nesten med en gang. En hurtigbufferfeil oppstår når den nødvendige koden ikke er på det laveste hurtigbuffernivået.

så en ny kode opprettes I l1-hurtigbufferen, og resten av prosessorarkitekturen tar over, jakter tilbake gjennom de andre hurtigbuffernivåene (helt tilbake til hovedlagringsstasjonen, om nødvendig) for å finne dataene for den taggen. Men for å få plass I l1-cachen for denne nye taggen, må noe annet alltid startes ut I L2.

dette resulterer i en nesten konstant shuffling om data, alt oppnådd i bare en håndfull klokkesykluser. Den eneste måten å oppnå dette på er å ha en kompleks struktur rundt SRAM, for å håndtere styringen av dataene. Sagt på en annen måte: HVIS EN CPU-kjerne besto av bare EN ALU, Ville l1-cachen være mye enklere, men siden det er dusinvis av dem (hvorav mange vil jonglere to tråder med instruksjoner), krever cachen flere tilkoblinger for å holde alt på farten.

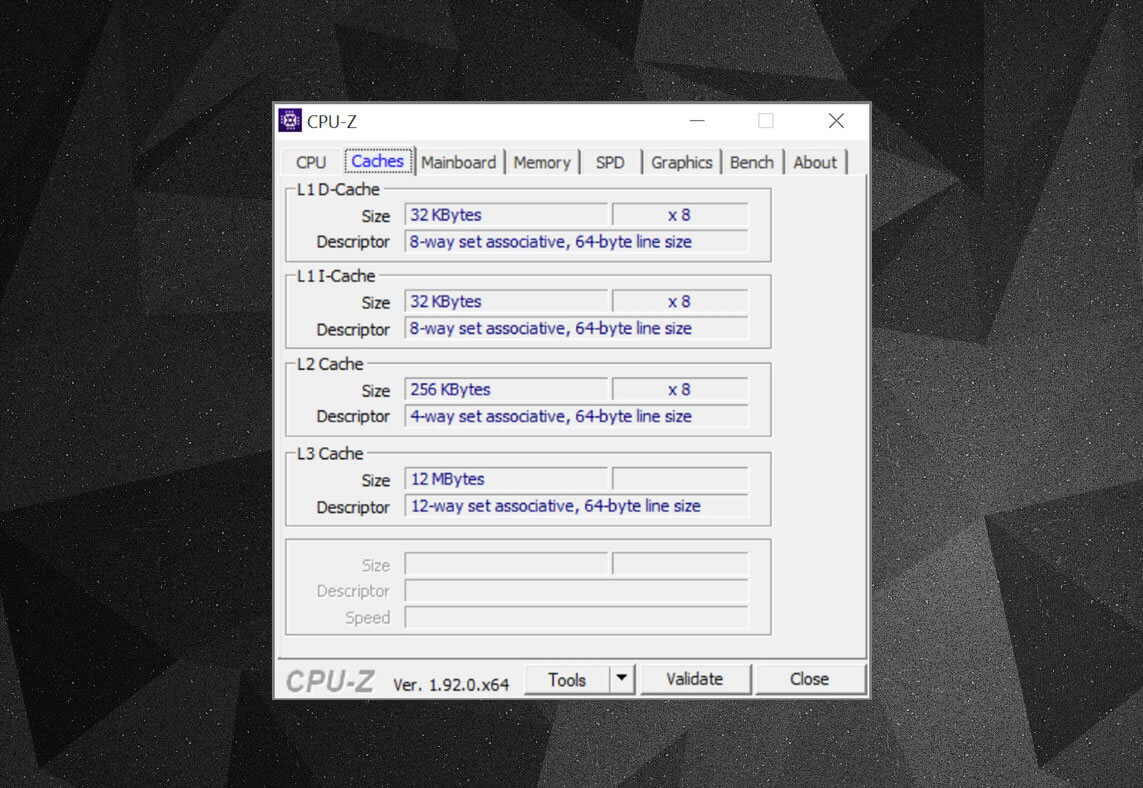

du kan bruke gratis programmer, FOR eksempel CPU-Z, for å sjekke ut cache informasjon for prosessoren slår din egen datamaskin. Men hva betyr all denne informasjonen? Et viktig element er etiketten sett assosiativ-dette handler om reglene håndheves av hvordan blokker av data fra systemminnet kopieres inn i hurtigbufferen.den ovennevnte cacheinformasjonen er For En Intel Core i7-9700K. Nivå 1-cachene er hver delt opp i 64 små blokker, kalt sett, og hver av disse er videre delt inn i cachelinjer (64 byte i størrelse). Sett assosiativ betyr at en blokk med data fra systemminnet er kartlagt på cache linjene i ett bestemt sett, snarere enn å være fri til å kartlegge over hvor som helst.

8-veisdelen forteller oss at en blokk kan knyttes til 8 cache linjer i et sett. Jo større nivået av assosiativitet (dvs. flere måter), desto bedre er sjansene for å få et cache-treff når CPUEN går på jakt etter data, og en reduksjon i straffen forårsaket av cache-savner. Ulempene er at det legger til mer kompleksitet, økt strømforbruk, og kan også redusere ytelsen fordi det er flere cache linjer å behandle for en blokk med data.

L1+L2 inkluderende cache, L3 offer cache, skrive-tilbake politikk, selv ECC. Kilde: Fritzchens Fritz

Et annet aspekt til kompleksiteten i cache dreier seg om hvordan data holdes på tvers av de ulike nivåene. Reglene er satt i noe som kalles inkluderingspolitikken. For Eksempel Har Intel Core-prosessorer fullt inkluderende l1 + L3 cache. Dette betyr at de samme dataene i Nivå 1, for eksempel, også kan være I Nivå 3. Dette kan virke som det er å kaste bort verdifull cache plass, men fordelen er at hvis prosessoren får en glipp, når du søker etter en kode i et lavere nivå, det trenger ikke å jakte gjennom høyere nivå for å finne den.

I de samme prosessorene er l2-hurtigbufferen ikke inkludert: alle data som er lagret der, kopieres ikke til noe annet nivå. Dette sparer plass, men resulterer i at chipens minnesystem må søke Gjennom L3 (som alltid er mye større) for å finne en savnet tag. Victim cacher ligner dette, men de er vant til lagret informasjon som blir presset ut av et lavere nivå-FOR EKSEMPEL BRUKER AMDS Zen 2-prosessorer L3 victim cache som bare lagrer data Fra L2.

Det finnes andre retningslinjer for cache, for eksempel når data blir skrevet inn i cache og hovedsystemet minne. Dette betyr at når data blir skrevet inn i et cache-nivå, er det en forsinkelse før systemminnet blir oppdatert med en kopi av det. For det meste går denne pause så lenge dataene forblir i hurtigbufferen-bare når DEN er startet, får RAM informasjonen.

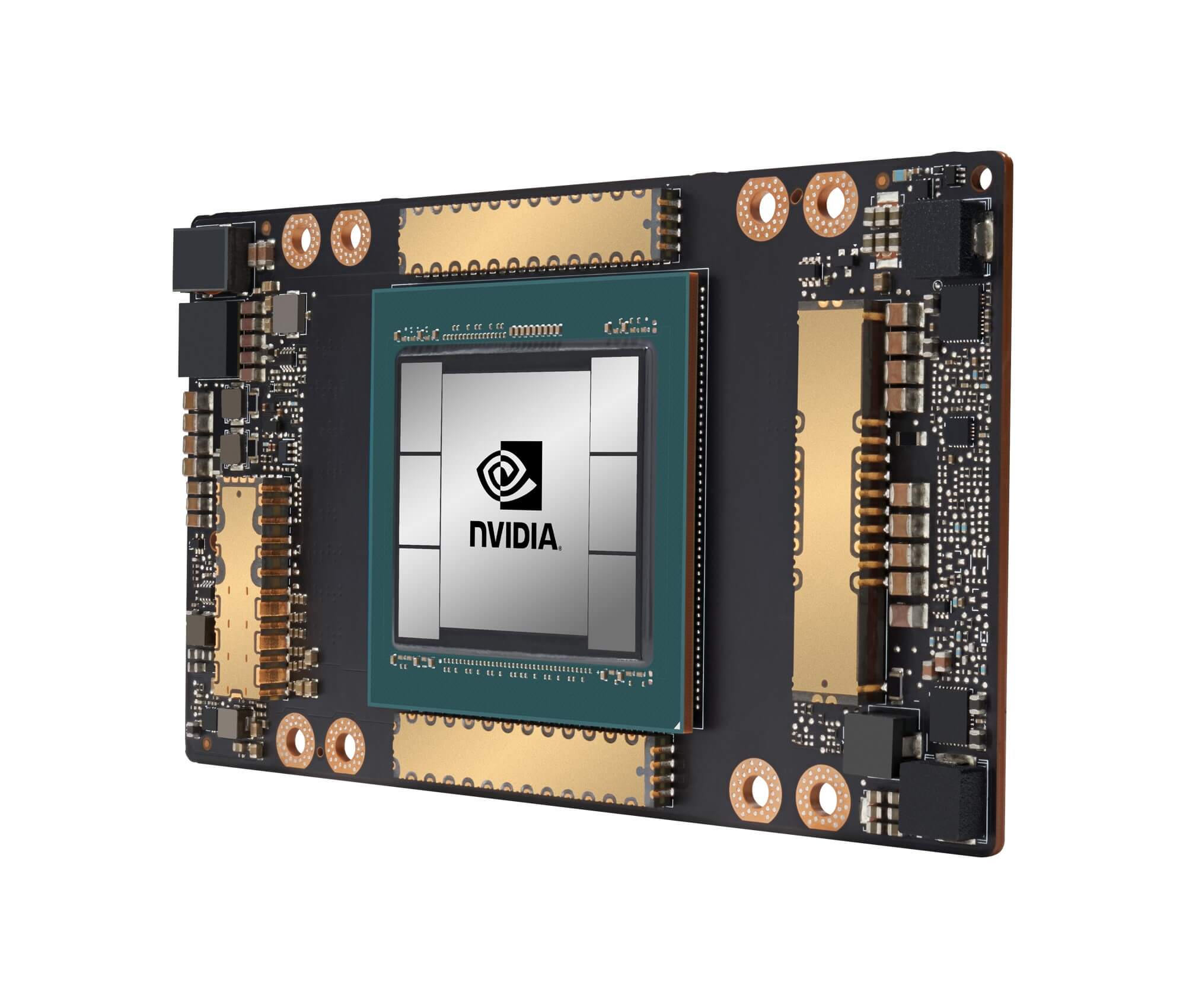

Nvidias GA100 grafikkprosessor, fullpakket med totalt 20 MB L1 og 40 MB L2 cache

for prosessordesignere handler valg av mengde, type og policy for cache om å balansere ønsket om større prosessorkapasitet mot økt kompleksitet og nødvendig dørplass. Hvis det var mulig å ha 20 MB, 1000-veis fullt assosiative Nivå 1 cacher uten at sjetongene blir Størrelsen På Manhattan (og bruker samme type kraft), så ville vi alle ha datamaskiner som har slike chips!

det laveste nivået av cacher i dagens Cpuer har ikke endret seg så mye i det siste tiåret. Nivå 3 cache har imidlertid fortsatt å vokse i størrelse. For ti år siden kunne du få 12 MB av det, hvis du var heldig nok til å eie En $ 999 Intel i7-980X. for halvparten av det beløpet i dag får du 64 MB.

Cache, i et nøtteskall: absolutt nødvendig, helt fantastisk biter av teknologi. Vi har ikke sett på andre cachetyper I Cpuer og Gpuer (for eksempel oversettelsesoppslagbuffere eller teksturbuffere), men siden de alle følger en enkel struktur og mønster av nivåer som vi har dekket her, vil de kanskje ikke høres så komplisert ut.

hadde du en datamaskin som hadde L2 cache på hovedkortet? Hva med de slot-baserte Pentium II OG Celeron Cpuer (f. eks. 300a) som kom i et datterbrett? Kan du huske din forste CPU som hadde delt L3? Gi oss beskjed i kommentarfeltet.

Shopping Snarveier:

- AMD Ryzen 9 3900x På Amazon

- AMD Ryzen 9 3950x På Amazon

- Intel Core i9-10900k På Amazon

- AMD Ryzen 7 3700x På Amazon

- Intel Core i7-10700k På Amazon

- AMD Ryzen 5 3600 På Amazon

- Intel Core i5-10600k på amazon

Fortsett å lese. Explainers På TechSpot

- Wi-Fi 6 Forklart: Neste Generasjon Wi-Fi

- Hva Er Tensor Kjerner?

- Hva Er Chip Binning?

Leave a Reply