Explainer: L1 vs.L2 vs. L3 Cache

fiecare CPU găsit în orice computer, de la un laptop ieftin la un server de milioane de dolari, va avea ceva numit cache. Cel mai probabil, va avea mai multe niveluri de ea, de asemenea.

trebuie să fie important, altfel de ce ar fi acolo? Dar ce face cache, și de ce nevoia de diferite niveluri de lucruri? Ce înseamnă chiar asociativul cu 12 căi?

ce este mai exact cache-ul?

TL;DR: este o memorie mică, dar foarte rapidă, care se află chiar lângă unitățile logice ale procesorului.

dar, desigur, există mult mai multe putem afla despre cache…

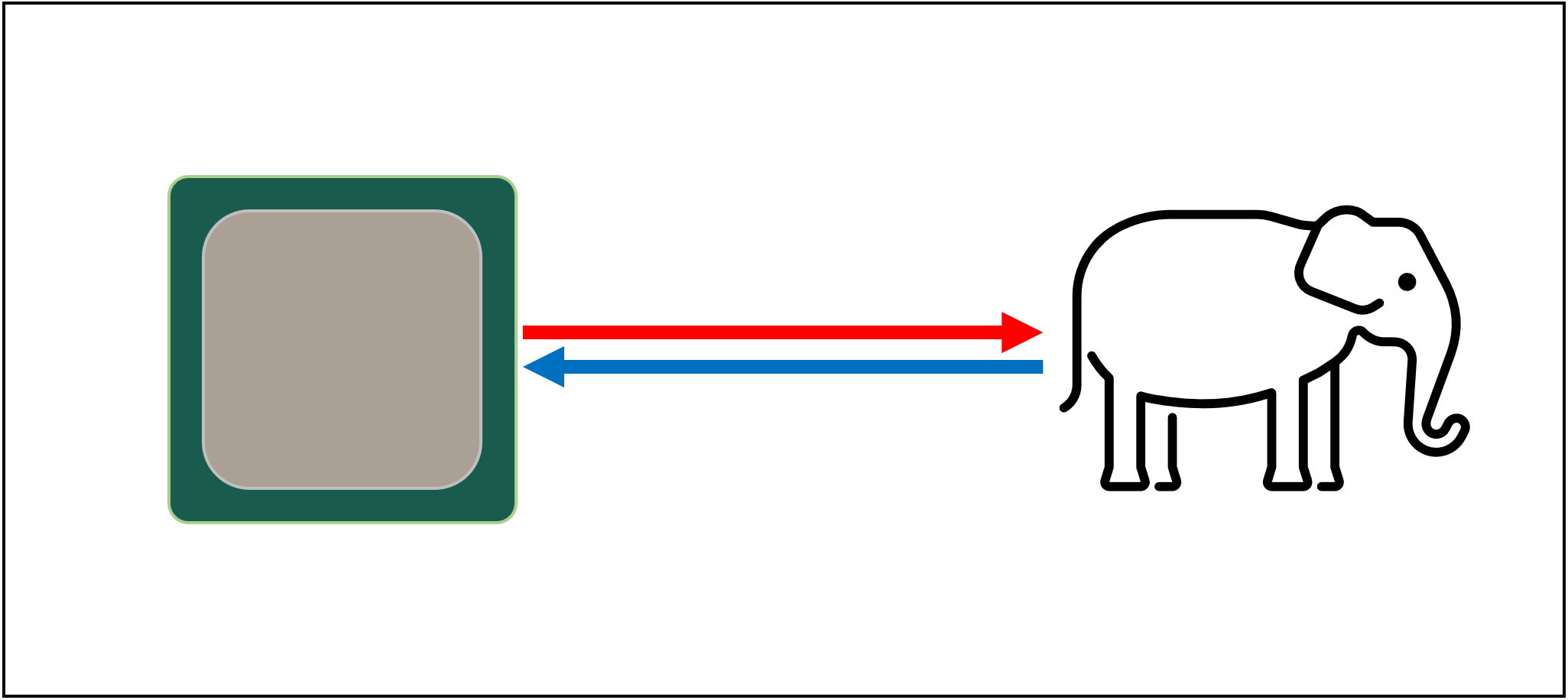

să începem cu un sistem de stocare imaginar, Magic: este infinit de rapid, poate gestiona un număr infinit de tranzacții de date simultan și păstrează întotdeauna datele în siguranță. Nu că există ceva chiar de la distanță, dar dacă ar fi, designul procesorului ar fi mult mai simplu.

procesoarele ar trebui să aibă doar unități logice pentru adăugare, înmulțire etc. și un sistem de gestionare a transferurilor de date. Acest lucru se datorează faptului că sistemul nostru teoretic de stocare poate trimite și primi instantaneu toate numerele necesare; niciuna dintre unitățile logice nu ar fi reținută în așteptarea unei tranzacții de date.

dar, după cum știm cu toții, nu există nicio tehnologie de stocare magică. În schimb, avem unități hard sau solid state și chiar și cele mai bune dintre acestea nu sunt capabile nici măcar de la distanță să gestioneze toate transferurile de date necesare pentru un procesor tipic.

Marele t ‘ Phon al stocării datelor

motivul pentru care este că procesoarele moderne sunt incredibil de rapide-iau doar un ciclu de ceas pentru a adăuga două valori întregi pe 64 de biți împreună, iar pentru un procesor care rulează la 4 GHz, acesta ar fi doar 0.0000000025 secunde sau un sfert de nanosecundă.

între timp, hard disk-urile care se învârt necesită mii de nanosecunde doar pentru a găsi date pe discurile din interior, să nu mai vorbim de transferul acestora, iar unitățile în stare solidă durează încă zeci sau sute de nanosecunde.

astfel de unități evident nu pot fi încorporate în procesoare, ceea ce înseamnă că va exista o separare fizică între cele două. Acest lucru doar adaugă mai mult timp pe mutarea de date, ceea ce face lucrurile chiar mai rău.

Marele a ‘ Tuin de stocare a datelor, din păcate

deci, ceea ce avem nevoie este un alt sistem de stocare a datelor, care se află între procesor și stocarea principală. Trebuie să fie mai rapid decât o unitate, să poată gestiona simultan o mulțime de transferuri de date și să fie mult mai aproape de procesor.

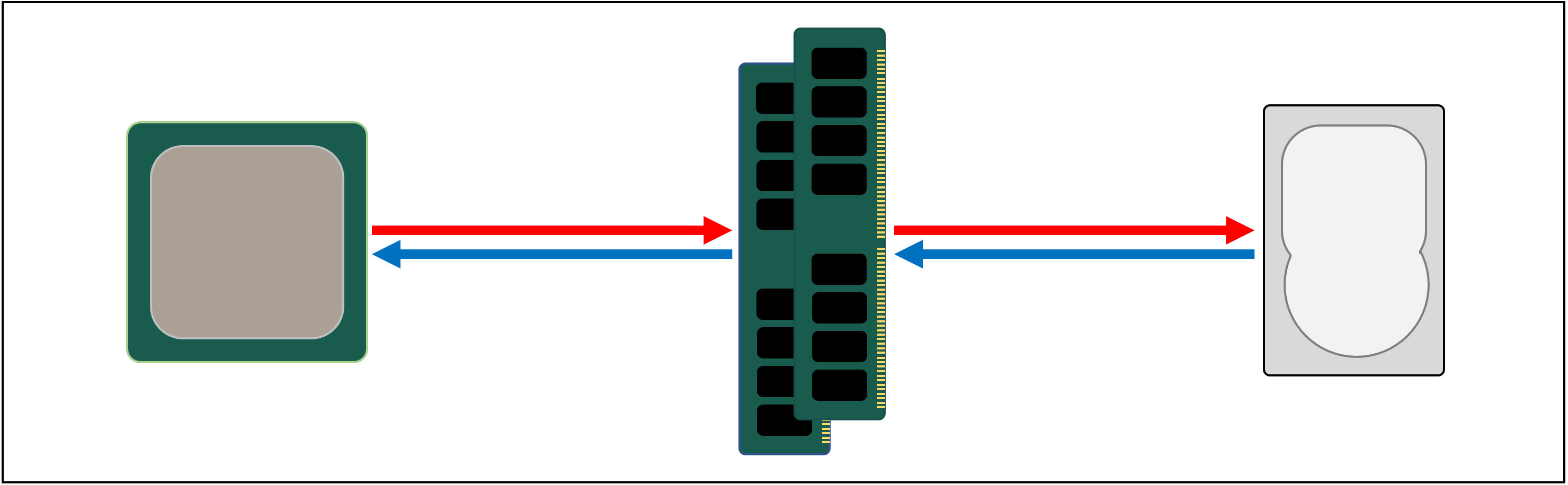

Ei bine, avem deja un astfel de lucru, și se numește RAM, și fiecare sistem informatic are unele pentru acest scop.aproape tot acest tip de stocare este DRAM (dynamic random access memory) și este capabil să transmită date mult mai rapid decât orice unitate.

cu toate acestea, în timp ce DRAM este foarte rapid, nu poate stoca oriunde în apropiere de cât mai multe date.

unele dintre cele mai mari cipuri de memorie DDR4 realizate de Micron, unul dintre puținii producători de DRAM, deține 32 Gbits sau 4 GB de date; cele mai mari hard disk-uri dețin de 4.000 de ori mai mult decât acesta.deci, deși am îmbunătățit viteza rețelei noastre de date, vor fi necesare sisteme suplimentare-hardware și software-pentru a afla ce date ar trebui păstrate în cantitatea limitată de DRAM, gata pentru CPU.

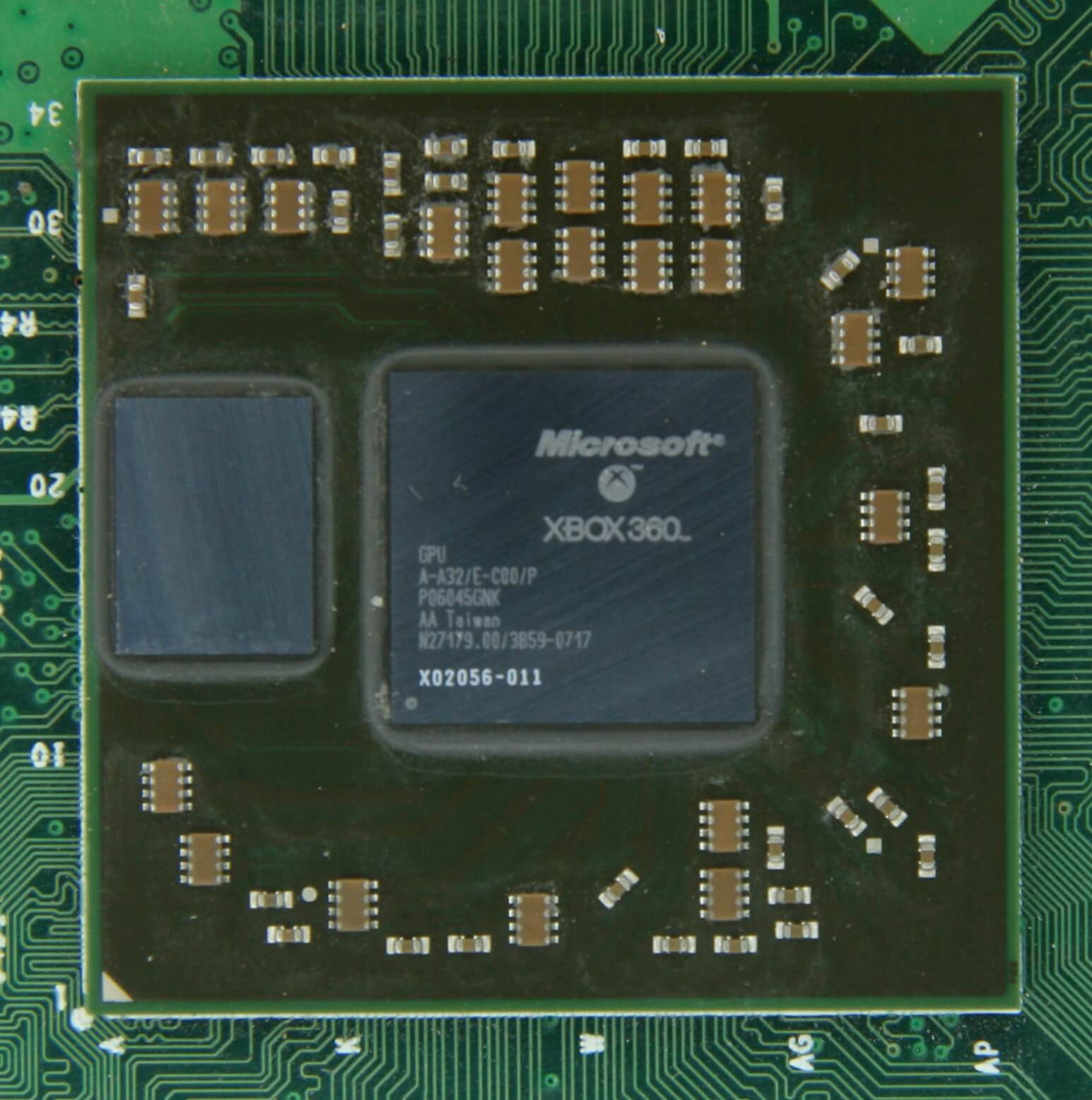

cel puțin DRAM poate fabricat pentru a fi în pachetul cip (cunoscut sub numele de Dram încorporat). Procesoarele sunt destul de mici, totuși, așa că nu puteți lipi atât de mult în ele.

10 MB de DRAM doar la stânga procesorului grafic Xbox 360. Sursa: CPU Grave Yard

marea majoritate a DRAM este situat chiar lângă procesor, conectat la placa de bază, și este întotdeauna cea mai apropiată componentă a procesorului, într-un sistem informatic. Și totuși, încă nu este suficient de rapid…DRAM mai are nevoie de aproximativ 100 de nanosecunde pentru a găsi date, dar cel puțin poate transfera miliarde de biți în fiecare secundă. Se pare că vom avea nevoie de o altă etapă de memorie, pentru a merge între unitățile procesorului și DRAM.

Enter stage left: SRAM (memorie cu acces aleatoriu static). În cazul în care DRAM utilizează condensatori microscopici pentru a stoca date sub formă de sarcină electrică, SRAM folosește tranzistoare pentru a face același lucru și acestea pot funcționa aproape la fel de repede ca unitățile logice dintr-un procesor (de aproximativ 10 ori mai rapid decât DRAM).

există, desigur, un dezavantaj pentru SRAM și încă o dată, este vorba despre spațiu.

memoria bazată pe tranzistor ocupă mult mai mult spațiu decât DRAM: pentru același cip de 4 GB DDR4, veți obține mai puțin de 100 MB în valoare de SRAM. Dar, deoarece este realizat prin același proces ca și crearea unui procesor, SRAM poate fi construit chiar în interiorul procesorului, cât mai aproape de unitățile logice posibil.

memoria bazată pe tranzistor ocupă mult mai mult spațiu decât DRAM: pentru același cip de 4 GB DDR4, veți obține mai puțin de 100 MB în valoare de SRAM.

cu fiecare etapă suplimentară, am crescut viteza de deplasare a datelor, la costul cât de mult putem stoca. Am putea continua adăugarea în mai multe secțiuni, fiecare fiind mai rapidă, dar mai mică.și astfel ajungem la o definiție mai tehnică a ceea ce este cache-ul: sunt mai multe blocuri de SRAM, toate situate în interiorul procesorului; sunt folosite pentru a se asigura că unitățile logice sunt ținute cât mai ocupate, prin trimiterea și stocarea datelor la viteze super rapide. Fericit cu asta? Bine-pentru că se va obține mult mai complicat de aici încolo!

Cache: o parcare pe mai multe niveluri

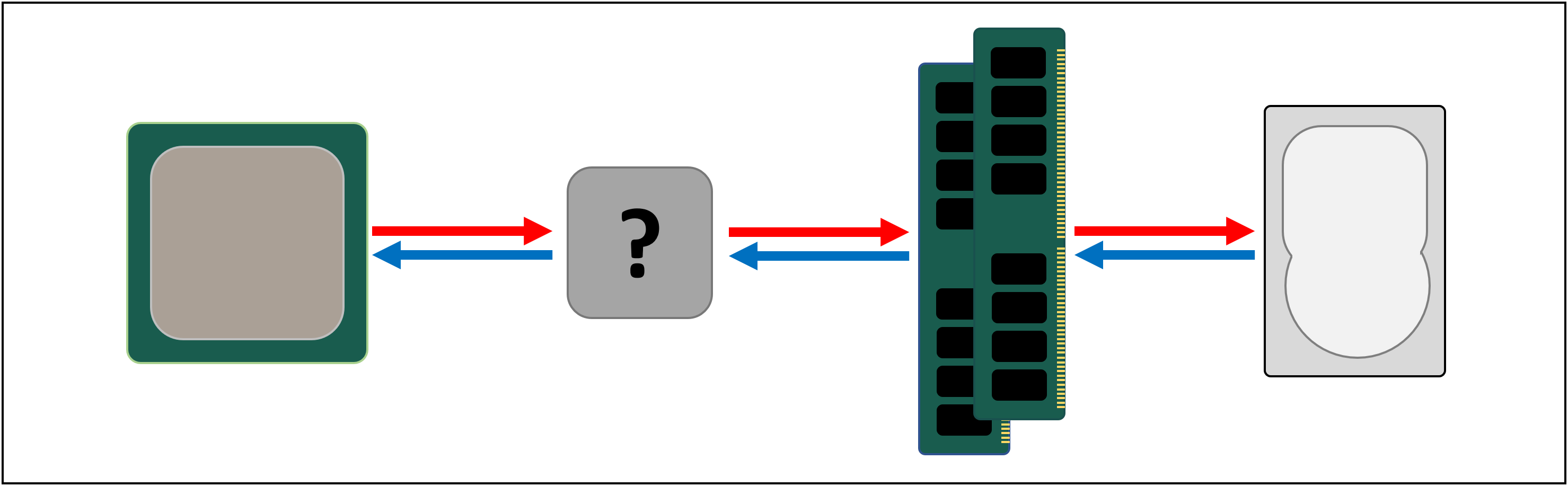

după cum am discutat, memoria cache este necesară deoarece nu există un sistem de stocare magic care să poată ține pasul cu cerințele de date ale unităților logice dintr-un procesor. Procesoarele moderne și procesoarele grafice conțin un număr de blocuri SRAM, care sunt organizate intern într-o ierarhie-o secvență de cache-uri care sunt ordonate după cum urmează:

în imaginea de mai sus, procesorul este reprezentat de dreptunghiul punctat negru. Alu (unități logice aritmetice) sunt în extrema stângă; acestea sunt structurile care alimentează procesorul, manipulând matematica pe care o face cipul. Deși din punct de vedere tehnic nu este cache, cel mai apropiat nivel de memorie de Alu sunt registrele (sunt grupate împreună într-un fișier de registru).

fiecare dintre acestea deține un singur număr, cum ar fi un număr întreg pe 64 de biți; valoarea în sine ar putea fi o bucată de date despre ceva, un cod pentru o instrucțiune specifică sau adresa de memorie a altor date.

fișierul de înregistrare într-un procesor desktop este destul de mic — de exemplu, în Intel Core i9-9900K, există două bănci ale acestora în fiecare nucleu, iar cel pentru numere întregi conține doar 180 de registre pe 64 de biți. Celălalt fișier de registru, pentru vectori (matrice mici de numere), are 168 intrări pe 256 de biți. Deci, fișierul total de înregistrare pentru fiecare nucleu este puțin sub 7 kB. Prin comparație, fișierul de registru din Multiprocesoarele de Streaming (echivalentul GPU al nucleului unui procesor) al unui Nvidia GeForce RTX 2080 Ti are o dimensiune de 256 kB.

registrele sunt SRAM, la fel ca cache-ul, dar sunt la fel de rapide ca Alu-urile pe care le servesc, împingând datele într-un singur ciclu de ceas. Dar nu sunt concepute pentru a stoca foarte multe date (doar o singură bucată din ele), motiv pentru care există întotdeauna câteva blocuri mai mari de memorie în apropiere: acesta este cache-ul de nivel 1.

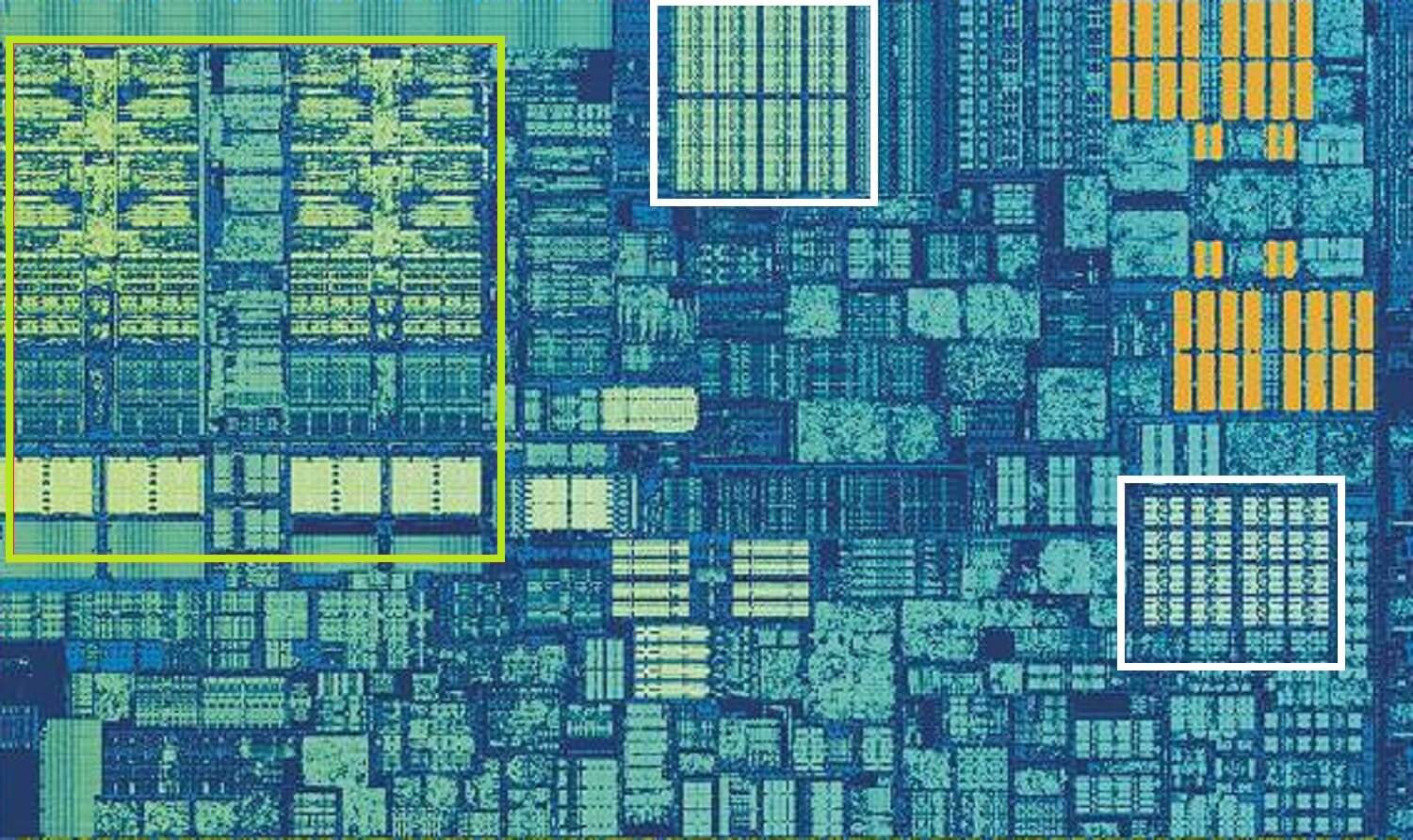

Intel Skylake CPU, mărită împușcat de un singur nucleu. Sursa: Wikichip

Imaginea de mai sus este o fotografie mărită a unui singur nucleu din designul procesorului Intel Skylake desktop.

Alu-urile și fișierele de registru pot fi văzute în extrema stângă, evidențiate în verde. În mijlocul de sus al imaginii, în alb, se află memoria cache de date de nivel 1. Acest lucru nu conține prea multe informații, doar 32 kB, dar, la fel ca registrele, este foarte aproape de unitățile logice și rulează cu aceeași viteză ca și ele.

celălalt dreptunghi alb indică cache-ul de instrucțiuni de nivel 1, de asemenea cu dimensiunea de 32 kB. După cum sugerează și numele, aceasta stochează diverse comenzi gata de a fi împărțite în așa-numitele micro-operații mai mici (de obicei etichetate ca octocops), pentru ca Alu-urile să le efectueze. Există și un cache pentru ei și îl puteți clasifica ca nivel 0, deoarece este mai mic (deținând doar 1.500 de operații) și mai aproape decât cache-urile L1.

s-ar putea să vă întrebați de ce aceste blocuri de SRAM sunt atât de mici; de ce nu au o dimensiune megabyte? Împreună, cache-urile de date și instrucțiuni ocupă aproape aceeași cantitate de spațiu în cip ca și principalele unități logice, astfel încât creșterea lor ar crește dimensiunea totală a matriței.dar principalul motiv pentru care dețin doar câțiva kB este că timpul necesar pentru găsirea și recuperarea datelor crește pe măsură ce capacitatea memoriei devine mai mare. Cache-ul L1 trebuie să fie foarte rapid și, prin urmare, trebuie atins un compromis, între dimensiune și viteză-în cel mai bun caz, este nevoie de aproximativ 5 cicluri de ceas (mai lungi pentru valorile în virgulă mobilă) pentru a obține datele din acest cache, gata de utilizare.

cache-ul L2 al lui Skylake: 256 kB de bunătate SRAM

dar dacă acesta ar fi singurul cache din interiorul unui procesor, atunci performanța sa ar lovi un perete brusc. Acesta este motivul pentru care toate au un alt nivel de memorie încorporat în nuclee: cache-ul de nivel 2. Acesta este un bloc general de stocare, care ține de instrucțiuni și date.

este întotdeauna destul de mult mai mare decât nivelul 1: procesoarele AMD Zen 2 împachetează până la 512 kB, astfel încât cache-urile de nivel inferior pot fi păstrate bine furnizate. Această dimensiune suplimentară are însă un cost și durează aproximativ de două ori mai mult pentru a găsi și transfera datele din acest cache, comparativ cu nivelul 1.

revenind în timp, la zilele originale Intel Pentium, nivelul 2 cache a fost un cip separat, fie pe un mic plug-in placa de circuit (ca un RAM DIMM) sau construit în placa de bază principală. În cele din urmă și-a făcut drum pe pachetul CPU în sine, până când a fost în cele din urmă integrat în matrița procesorului, în genul procesoarelor Pentium III și AMD K6-III.

această dezvoltare a fost urmată în curând de un alt nivel de cache, acolo pentru a sprijini celelalte niveluri inferioare, și a apărut ca urmare a creșterii de chips-uri multi-core.

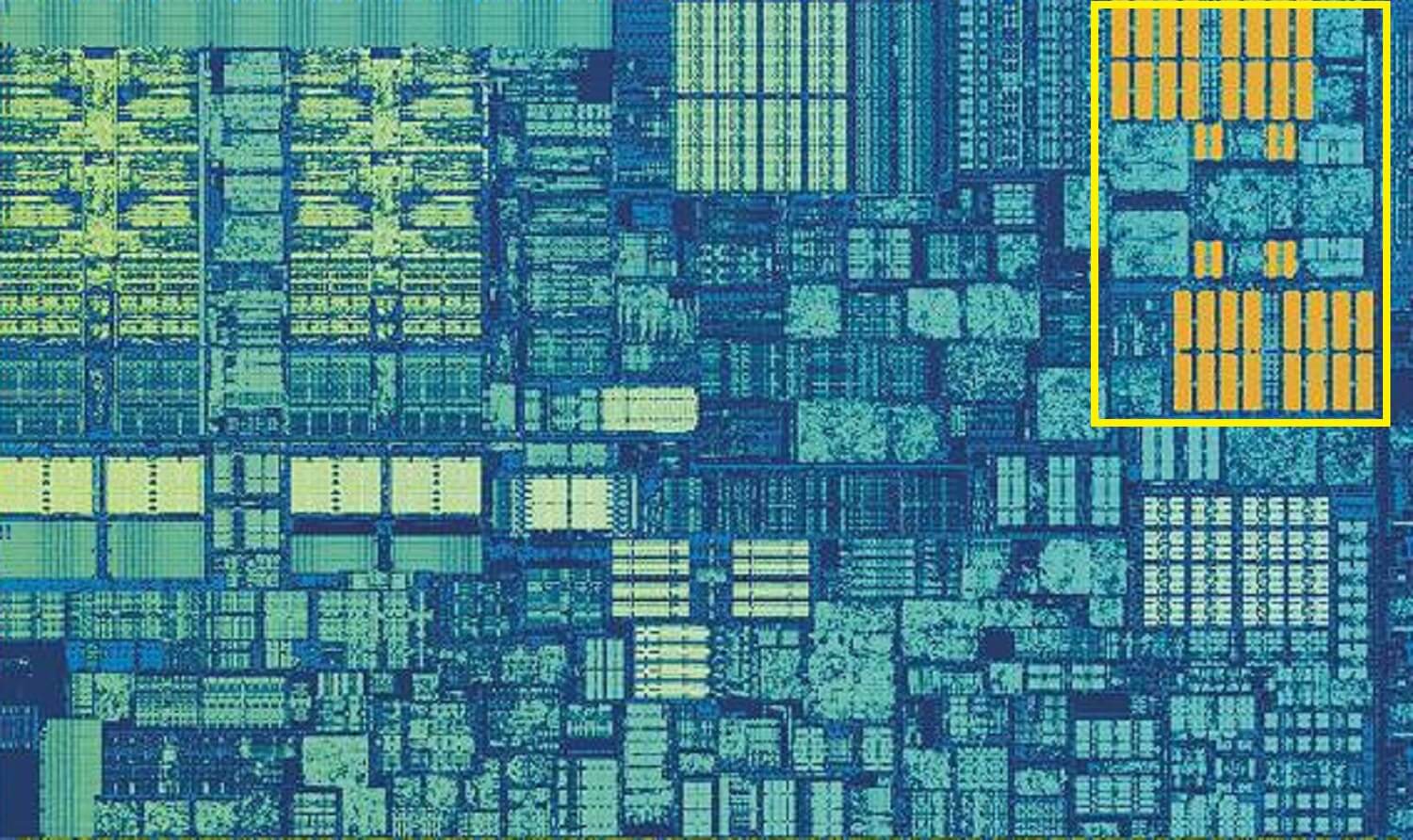

cip Intel Kaby Lake. Sursa: Wikichip

această imagine, a unui cip Intel Kaby Lake, Arată 4 nuclee în stânga-mijloc (un GPU integrat ocupă aproape jumătate din matriță, în dreapta). Fiecare nucleu are propriul set ‘privat’ de cache-uri de nivel 1 și 2 (evidențieri albe și galbene), dar vin și cu un al treilea set de blocuri SRAM.nivelul 3 cache, chiar dacă este direct în jurul unui singur nucleu, este complet partajat cu ceilalți-fiecare poate accesa liber conținutul cache-ului L3 al altuia. Este mult mai mare (între 2 și 32 MB), dar și mult mai lent, în medie peste 30 de cicluri, mai ales dacă un nucleu trebuie să utilizeze date care se află într-un bloc de cache la o anumită distanță.

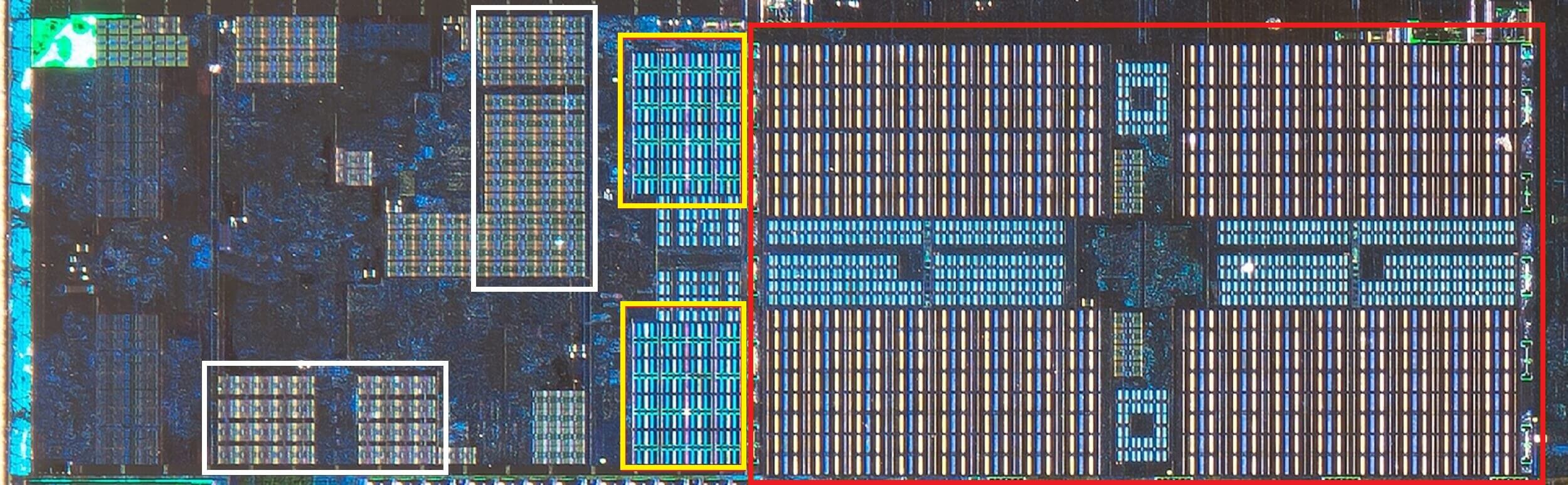

mai jos, putem vedea un singur nucleu în arhitectura Zen 2 AMD: cache-urile de date și instrucțiuni de nivel 32 kB 1 în alb, nivelul 512 KB 2 în galben și un bloc enorm de 4 MB de cache L3 în roșu.

AMD Zen 2 CPU, mărită împușcat de un singur nucleu. Sursa: Fritzchens Fritz

așteptați o secundă. Cum poate 32 kB să ocupe mai mult spațiu fizic decât 512 kB? Dacă nivelul 1 conține atât de puține date, de ce este proporțional mult mai mare decât cache-ul L2 sau L3?

mai mult decât un număr

Cache crește performanța prin accelerarea transferului de date către unitățile logice și păstrarea în apropiere a unei copii a instrucțiunilor și datelor utilizate frecvent. Informațiile stocate în memoria cache sunt împărțite în două părți: datele în sine și locația în care au fost localizate inițial în memoria/stocarea sistemului-această adresă se numește etichetă cache.

când CPU rulează o operație care dorește să citească sau să scrie date din / în memorie, începe prin verificarea etichetelor din memoria cache de nivel 1. Dacă este prezentă cea necesară (o lovitură cache), aceste date pot fi accesate aproape imediat. O lipsă de cache apare atunci când eticheta necesară nu se află la cel mai scăzut nivel de cache.

deci, o nouă etichetă este creată în cache-ul L1, iar restul arhitecturii procesorului preia, vânând înapoi prin celelalte niveluri de cache (până la unitatea principală de stocare, dacă este necesar) pentru a găsi datele pentru acea etichetă. Dar pentru a face spațiu în memoria cache L1 pentru această nouă etichetă, altceva trebuie invariabil să fie pornit în L2.

Acest lucru duce la o amestecare aproape constantă a datelor, toate realizate în doar o mână de cicluri de ceas. Singura modalitate de a realiza acest lucru este de a avea o structură complexă în jurul SRAM, să se ocupe de gestionarea datelor. Pune un alt mod: dacă un nucleu CPU ar consta dintr-un singur ALU, atunci memoria cache L1 ar fi mult mai simplă, dar din moment ce există zeci dintre ele (dintre care multe vor jongla două fire de instrucțiuni), memoria cache necesită mai multe conexiuni pentru a menține totul în mișcare.

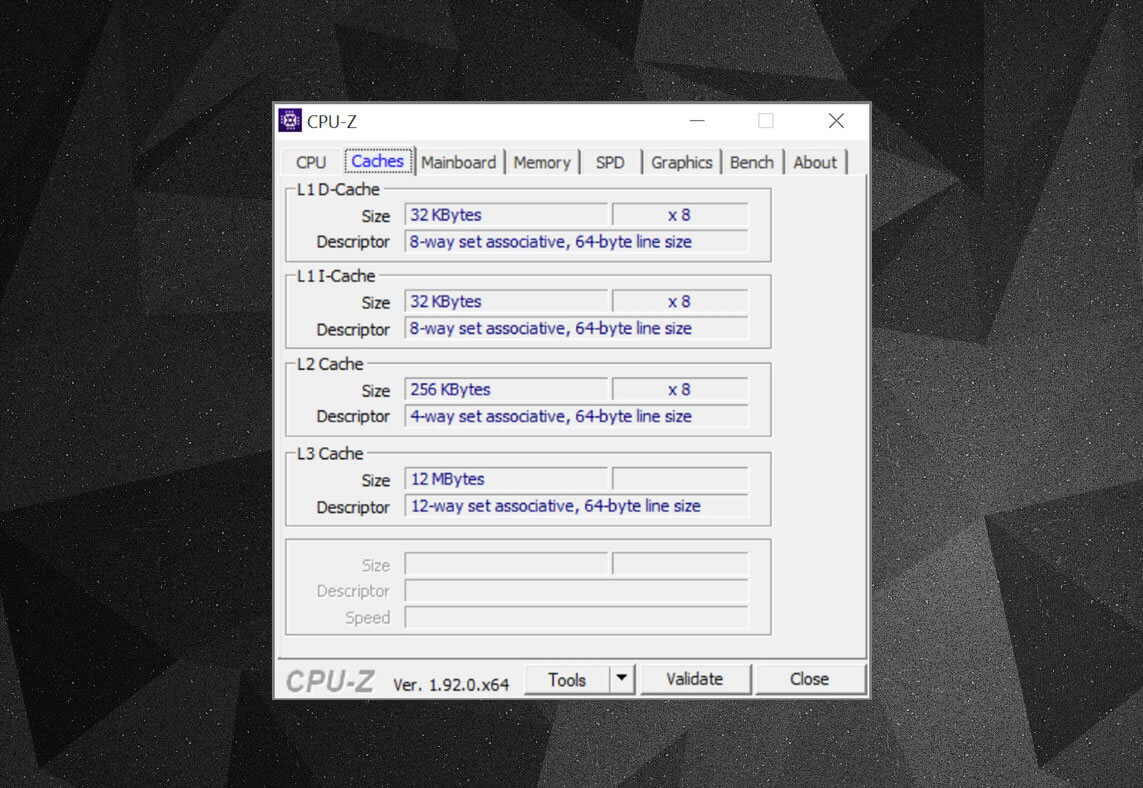

puteți utiliza programe gratuite, cum ar fi CPU-Z, pentru a verifica informațiile cache pentru procesorul care alimentează propriul computer. Dar ce înseamnă toate aceste informații? Un element important este setul de etichete asociativ – este vorba despre regulile aplicate de modul în care blocurile de date din memoria sistemului sunt copiate în memoria cache.

informațiile cache de mai sus sunt pentru un Intel Core i7-9700K. cache-urile sale de nivel 1 sunt împărțite fiecare în 64 de blocuri mici, numite seturi și fiecare dintre acestea este împărțită în linii cache (64 octeți în dimensiune). Set Asociativ înseamnă că un bloc de date din memoria sistemului este mapat pe liniile cache dintr-un anumit set, mai degrabă decât să fie liber să mapeze oriunde.

partea cu 8 căi ne spune că un bloc poate fi asociat cu 8 linii cache dintr-un set. Cu cât este mai mare nivelul de asociativitate (adică mai multe moduri), cu atât sunt mai mari șansele de a obține un cache lovit atunci când CPU merge la vânătoare de date și o reducere a penalităților cauzate de ratările cache-ului. Dezavantajele sunt că adaugă mai multă complexitate, un consum crescut de energie și poate, de asemenea, să scadă performanța, deoarece există mai multe linii de cache de procesat pentru un bloc de date.

L1+L2 inclusiv cache, L3 victima cache, scrie-back politici, chiar ECC. Sursa: Fritzchens Fritz

un alt aspect al complexității cache-ului se învârte în jurul modului în care datele sunt păstrate pe diferite niveluri. Regulile sunt stabilite în ceva numit politica de incluziune. De exemplu, procesoarele Intel Core au cache L1+L3 complet inclus. Aceasta înseamnă că aceleași date din Nivelul 1, de exemplu, pot fi și la nivelul 3. Acest lucru ar putea părea că pierde spațiu cache valoros, dar avantajul este că, dacă procesorul primește o ratare, atunci când caută o etichetă la un nivel inferior, nu trebuie să vâneze prin nivelul superior pentru a o găsi.

în aceleași procesoare, memoria cache L2 nu include: orice date stocate acolo nu sunt copiate la niciun alt nivel. Acest lucru economisește spațiu, dar are ca rezultat sistemul de memorie al cipului care trebuie să caute prin L3 (care este întotdeauna mult mai mare) pentru a găsi o etichetă ratată. Cache-urile victimelor sunt similare cu aceasta, dar sunt obișnuite cu informațiile stocate care sunt împinse dintr-un nivel inferior-de exemplu, procesoarele Zen 2 ale AMD utilizează memoria cache L3 care stochează doar date de la L2.

există și alte politici pentru memoria cache, cum ar fi atunci când datele sunt scrise în memoria cache și în memoria principală a sistemului. Acestea se numesc Politici de scriere și majoritatea procesoarelor de astăzi utilizează cache-uri de scriere înapoi; acest lucru înseamnă că atunci când datele sunt scrise într-un nivel de cache, există o întârziere înainte ca memoria sistemului să fie actualizată cu o copie a acesteia. În cea mai mare parte, această Pauză Rulează atât timp cât datele rămân în memoria cache-doar după ce sunt pornite, memoria RAM obține informațiile.

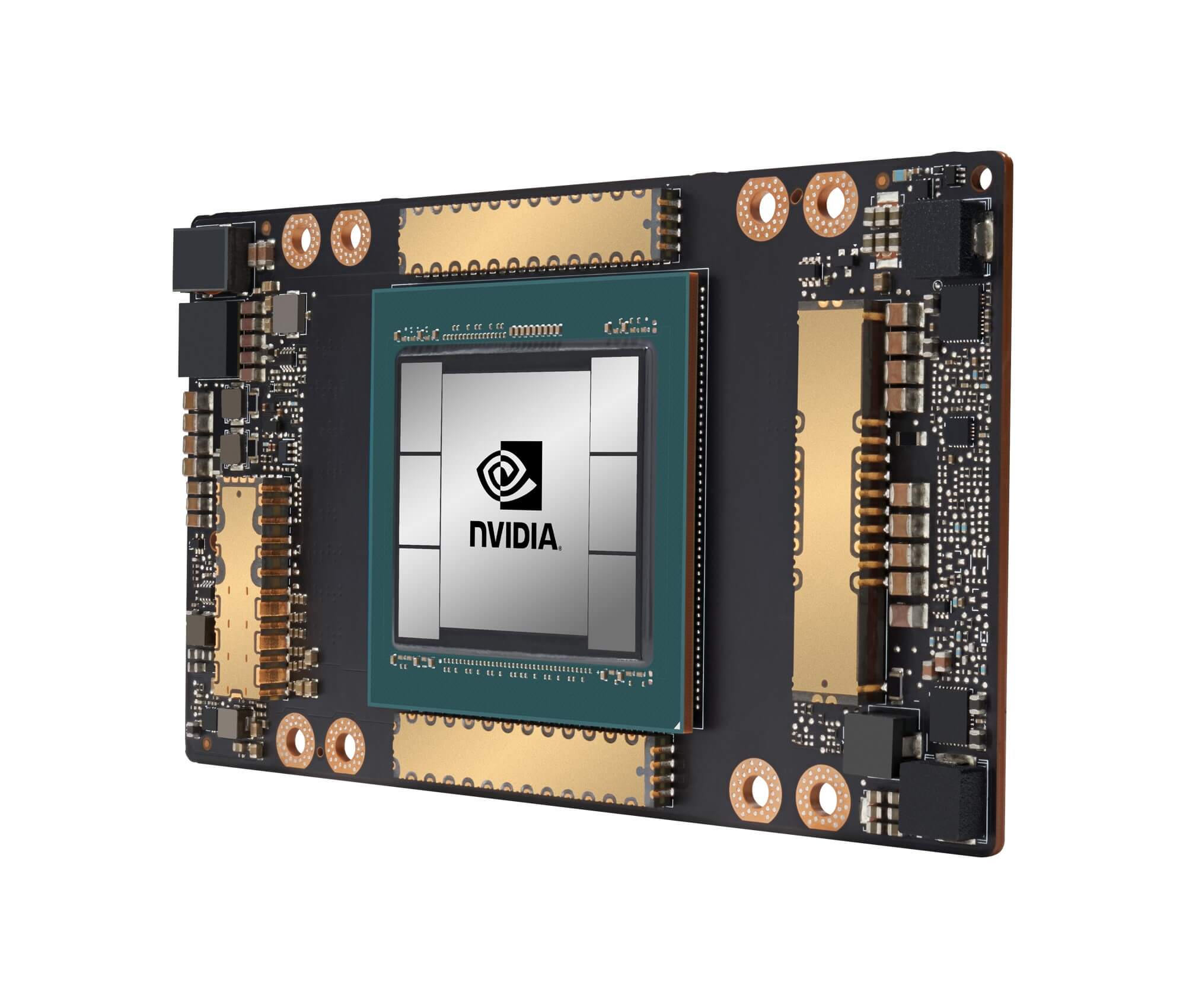

procesorul grafic NVIDIA GA100, dotat cu un total de 20 MB de L1 și 40 MB de cache L2

pentru proiectanții de procesoare, alegerea cantității, tipului și Politicii cache-ului se referă la echilibrarea dorinței pentru o capacitate mai mare a procesorului împotriva complexității crescute și a spațiului necesar. Dacă ar fi posibil să avem cache-uri de 20 MB, 1000-way complet asociative de nivel 1, fără ca jetoanele să devină de dimensiunea Manhattanului (și să consume același tip de putere), atunci am avea cu toții computere sportive de astfel de Jetoane!

cel mai scăzut nivel de cache-uri din procesoarele de astăzi nu s-au schimbat atât de mult în ultimul deceniu. Cu toate acestea, cache-ul de nivel 3 a continuat să crească în dimensiune. Un deceniu în urmă, ai putea obține 12 MB de ea, dacă ai fost destul de norocos să dețină un $999 Intel i7-980X. pentru jumătate din această sumă astăzi, veți obține 64 MB.

Cache, pe scurt: absolut necesare, absolut minunat piese de tehnologie. Nu ne-am uitat la alte tipuri de cache-uri din procesoare și GPU-uri (cum ar fi tampoanele de căutare a traducerilor sau cache-urile de textură), dar din moment ce toate urmează o structură simplă și un model de niveluri așa cum am acoperit aici, probabil că nu vor suna atât de complicat.

dețineți un computer care avea cache L2 pe placa de bază? Ce zici de acele procesoare Pentium II și Celeron bazate pe slot (de exemplu, 300a) care au venit într-un daughterboard? Vă puteți aminti primul procesor care a împărtășit L3? Spuneți-ne în secțiunea de comentarii.

comenzi rapide pentru cumpărături:

- AMD Ryzen 9 3900X pe Amazon

- AMD Ryzen 9 3950x pe Amazon

- Intel Core i9-10900k pe Amazon

- AMD Ryzen 7 3700x pe Amazon

- Intel Core i7-10700k pe Amazon

- AMD Ryzen 5 3600 pe Amazon

- Intel Core i5-10600k pe Amazon

continuați să citiți. Explicatori la TechSpot

- Wi-Fi 6 a explicat: următoarea generație de Wi-Fi

- ce sunt nucleele Tensor?

- ce este Chip Binning?

Leave a Reply