Explainer: L1 vs. L2 vs. L3 Cache

cada CPU encontrada em qualquer computador, de um laptop barato para um servidor de milhões de dólares, terá algo chamado cache. É mais provável que tenha vários níveis.deve ser importante, caso contrário porque estaria lá? Mas o que faz o cache, e por que a necessidade de diferentes níveis do material? O que significa associativa de 12 vias?

o que é exactamente a ‘cache’?

TL;DR: é uma memória pequena, mas muito rápida que fica ao lado das unidades lógicas da CPU.mas é claro, há muito mais que podemos aprender sobre cache…

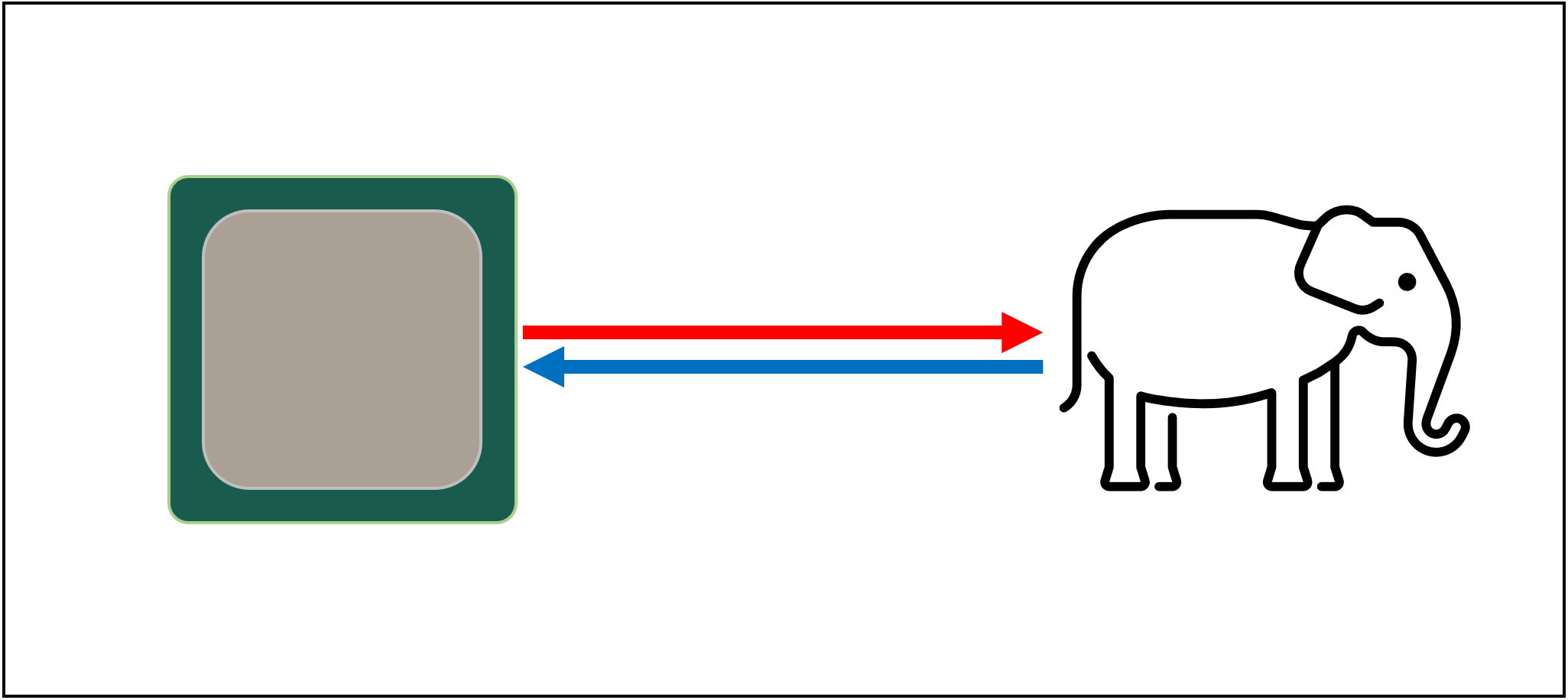

vamos começar com um sistema de armazenamento imaginário e mágico: é infinitamente rápido, pode lidar com um número infinito de transações de dados ao mesmo tempo, e sempre mantém os dados seguros e seguros. Não que nada remotamente exista, mas se existisse, o design do processador seria muito mais simples.

CPUs só precisaria de ter unidades lógicas para adicionar, multiplicar, etc. e um sistema para lidar com as transferências de dados. Isto porque o nosso sistema de armazenamento teórico pode enviar e receber instantaneamente todos os números necessários; nenhuma das unidades lógicas seria mantida esperando por uma transação de dados.mas, como todos sabemos, não há tecnologia de armazenamento de magia. Em vez disso, temos unidades de estado rígido ou sólido, e mesmo o melhor destes não são nem remotamente capazes de lidar com todas as transferências de dados necessárias para uma CPU típica.

O Grande T’Phon de armazenamento de dados

A razão é que os processadores modernos são incrivelmente rápido, pois levam apenas um ciclo de relógio para somar dois valores inteiros de 64 bits juntos, e para uma CPU rodando a 4 GHz, este seria apenas 0.00000000025 segundos ou um quarto de nanossegundo.enquanto isso, discos rígidos de fiação levam milhares de nanossegundos apenas para encontrar dados nos discos dentro, quanto mais transferi-los, e unidades de Estado Sólido ainda levam dezenas ou centenas de nanossegundos.

tais unidades obviamente não podem ser construídas em processadores, o que significa que haverá uma separação física entre os dois. Isto apenas acrescenta mais tempo ao movimento de dados, tornando as coisas ainda piores.

O Grande’Tuin de armazenamento de dados, infelizmente

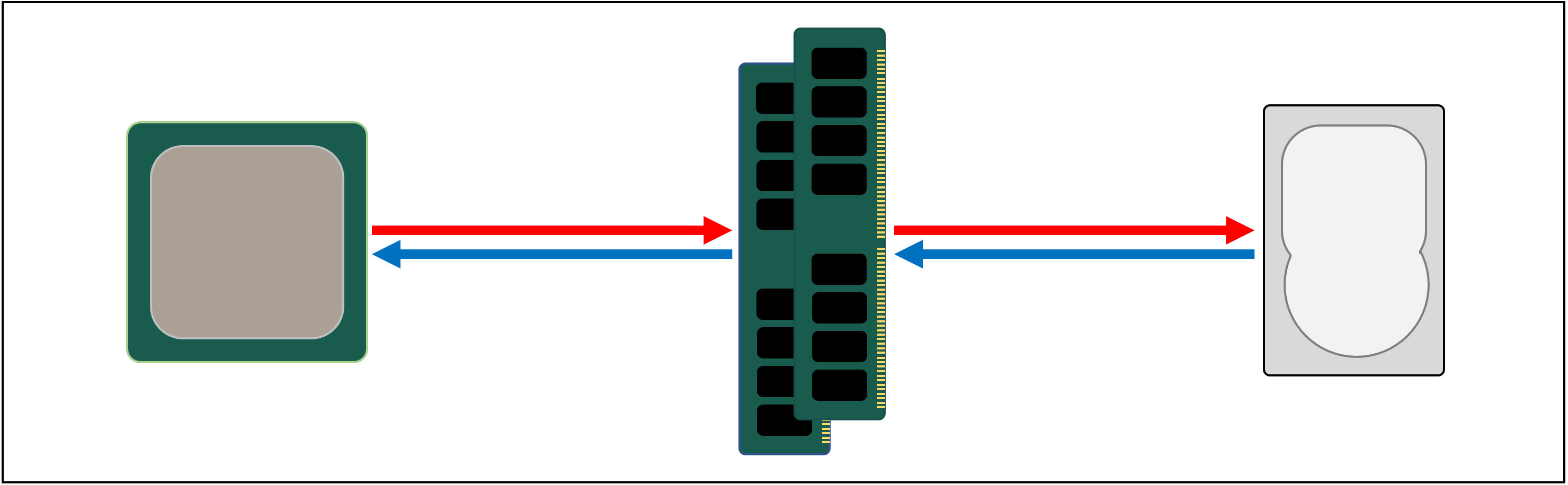

Então, o que precisamos é de um outro sistema de armazenamento de dados, que fica entre o processador e a memória principal. Precisa ser mais rápido do que uma unidade, ser capaz de lidar com muitas transferências de dados simultaneamente, e estar muito mais perto do processador.

Well, we already have such a thing, and it’s called RAM, and every computer system has some for this very purpose.

quase todo este tipo de armazenamento é DRAM (memória dinâmica de acesso Aleatório) e é capaz de passar dados em torno muito mais rápido do que qualquer unidade.

alguns dos maiores chips de memória DDR4 feitos pela Micron, um dos poucos fabricantes de DRAM, possui 32 Gbits ou 4 GB de dados; os maiores discos rígidos possuem 4.000 vezes mais do que isso.

assim, embora tenhamos melhorado a velocidade da nossa rede de dados, sistemas adicionais — hardware e software — serão necessários para determinar quais os dados que devem ser mantidos na quantidade limitada de DRAM, prontos para a CPU.

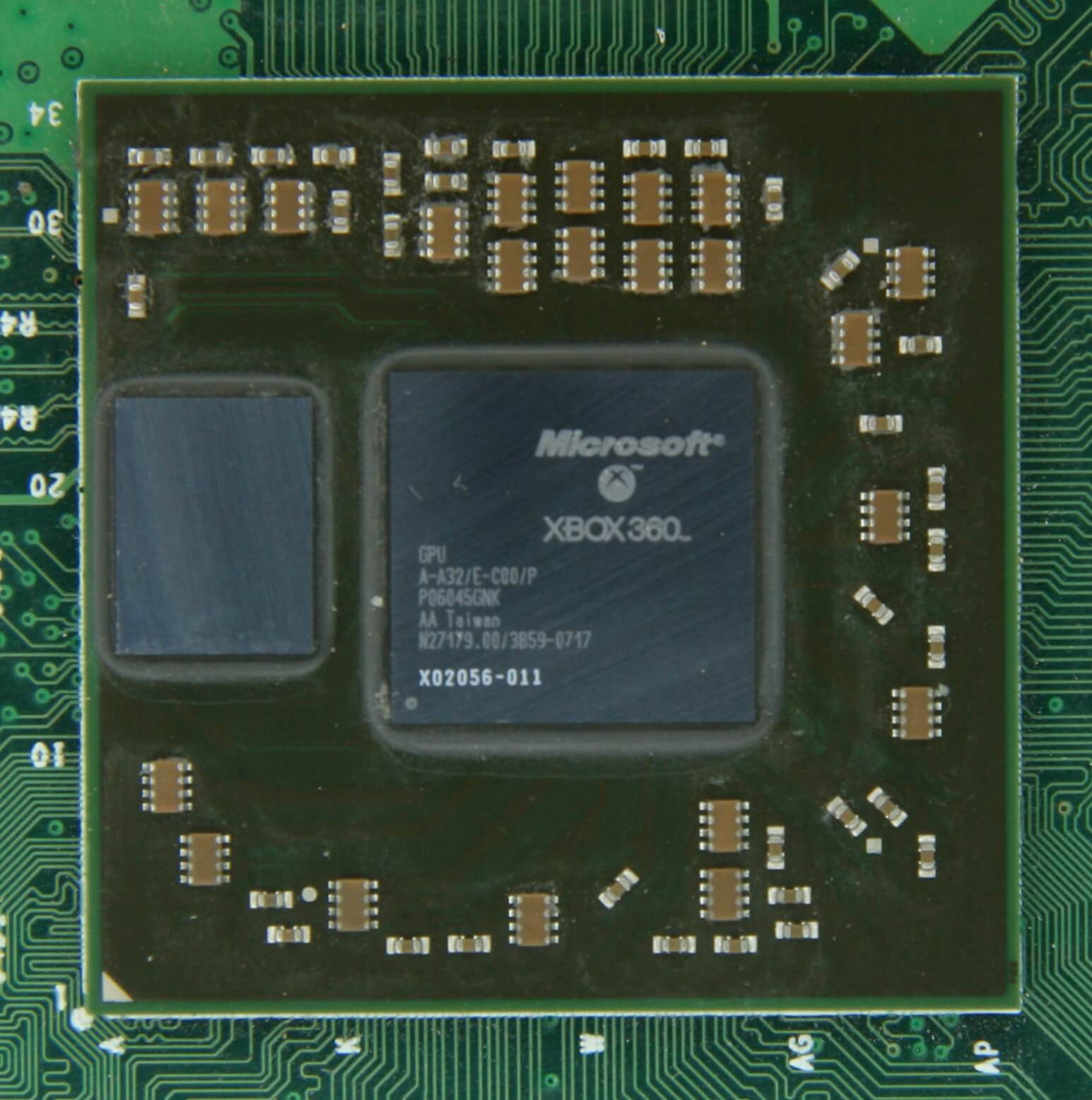

pelo menos as DRAM podem ser fabricadas para serem incluídas no pacote de chips (conhecidas como DRAM incorporadas). Mas os CPUs são muito pequenos, por isso não se pode enfiá-los assim tanto.

10 MB de DRAM apenas à esquerda do processador gráfico do Xbox 360. Fonte: CPU Grave Yard

A grande maioria das DRAM está localizada ao lado do processador, conectado à placa-mãe, e é sempre o componente mais próximo da CPU, em um sistema de computador. E ainda assim, não é rápido o suficiente…

DRAM ainda leva cerca de 100 nanossegundos para encontrar dados, mas pelo menos pode transferir bilhões de bits a cada segundo. Parece que vamos precisar de outro estágio de memória, para entrar entre as unidades do processador e o DRAM.

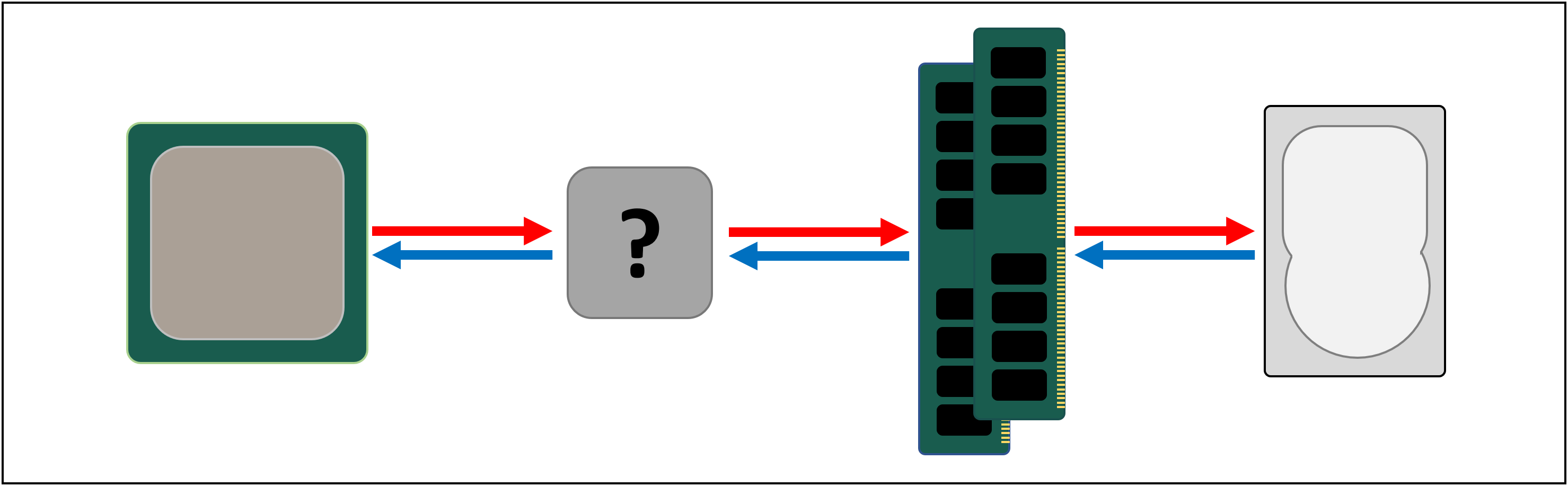

Enter stage left: SRAM (static random access memory). Onde DRAM usa capacitores microscópicos para armazenar dados na forma de carga elétrica, SRAM usa transistores para fazer a mesma coisa e estes podem funcionar quase tão rápido como as unidades lógicas em um processador (cerca de 10 vezes mais rápido que DRAM).

Existe, é claro, uma desvantagem para SRAM e, mais uma vez, é sobre o espaço.

a memória baseada em transistores ocupa muito mais espaço do que o DRAM: para o mesmo chip de 4 GB DDR4, você obteria menos de 100 MB de SRAM. Mas como é feito através do mesmo processo que criar uma CPU, o SRAM pode ser construído dentro do processador, o mais próximo possível das unidades lógicas.

a memória baseada em transistores ocupa muito mais espaço do que o DRAM: para o mesmo chip de 4 GB DDR4, você obteria menos de 100 MB de SRAM.

com cada etapa extra, aumentamos a velocidade de mover os dados, para o custo de quanto podemos armazenar. Poderíamos continuar a acrescentar mais secções, sendo cada uma mais rápida, mas mais pequena.

E assim chegamos a uma definição mais técnica do que cache É: são vários blocos de SRAM, todos localizados dentro do processador; eles são usados para garantir que as unidades lógicas são mantidas o mais ocupadas possível, enviando e armazenando dados em velocidades super rápidas. Contente com isso? Óptimo, porque vai ficar muito mais complicado a partir de agora!Cache

: um estacionamento multi-nível

como discutimos, cache é necessário porque não há um sistema de armazenamento mágico que possa acompanhar as exigências de dados das unidades lógicas em um processador. CPUs modernas e processadores gráficos contêm um número de SRAM blocos, que são internamente organizados em uma hierarquia — uma sequência de caches que são ordenadas da seguinte forma:

Na imagem acima, a CPU é representado pelo retângulo tracejado branco. O ALUs (unidades lógicas aritméticas) estão no Extremo Esquerdo; estas são as estruturas que alimentam o processador, lidando com a matemática que o chip faz. Enquanto seu cache tecnicamente não é, o nível de memória mais próximo ao ALUs são os registros (eles são agrupados em um arquivo de registro).

cada um destes contém um único número, como um inteiro de 64 bits; o valor em si pode ser um pedaço de dados sobre algo, um código para uma instrução específica, ou o endereço de memória de alguns outros dados.

o ficheiro de registo numa CPU desktop é bastante pequeno — por exemplo, no núcleo da Intel i9-9900K, existem dois bancos deles em cada núcleo, e o dos inteiros contém apenas 180 registos de 64 bits. O outro arquivo de registro, para vetores (pequenas matrizes de Números), tem 168 entradas de 256 bits. Então o arquivo Total de registro para cada núcleo é um pouco abaixo de 7 kB. Por comparação, o arquivo de registro nos multiprocessadores Streaming (o equivalente da GPU de um núcleo da CPU) de um NVIDIA GeForce RTX 2080 Ti é de 256 kB em tamanho.

registradores são SRAM, assim como cache, mas eles são tão rápidos quanto o ALUs que servem, empurrando dados para dentro e para fora em um único ciclo de clock. Mas eles não são projetados para armazenar Muito dados (apenas um único pedaço dele), e é por isso que há sempre alguns blocos maiores de memória perto: este é o cache de Nível 1.

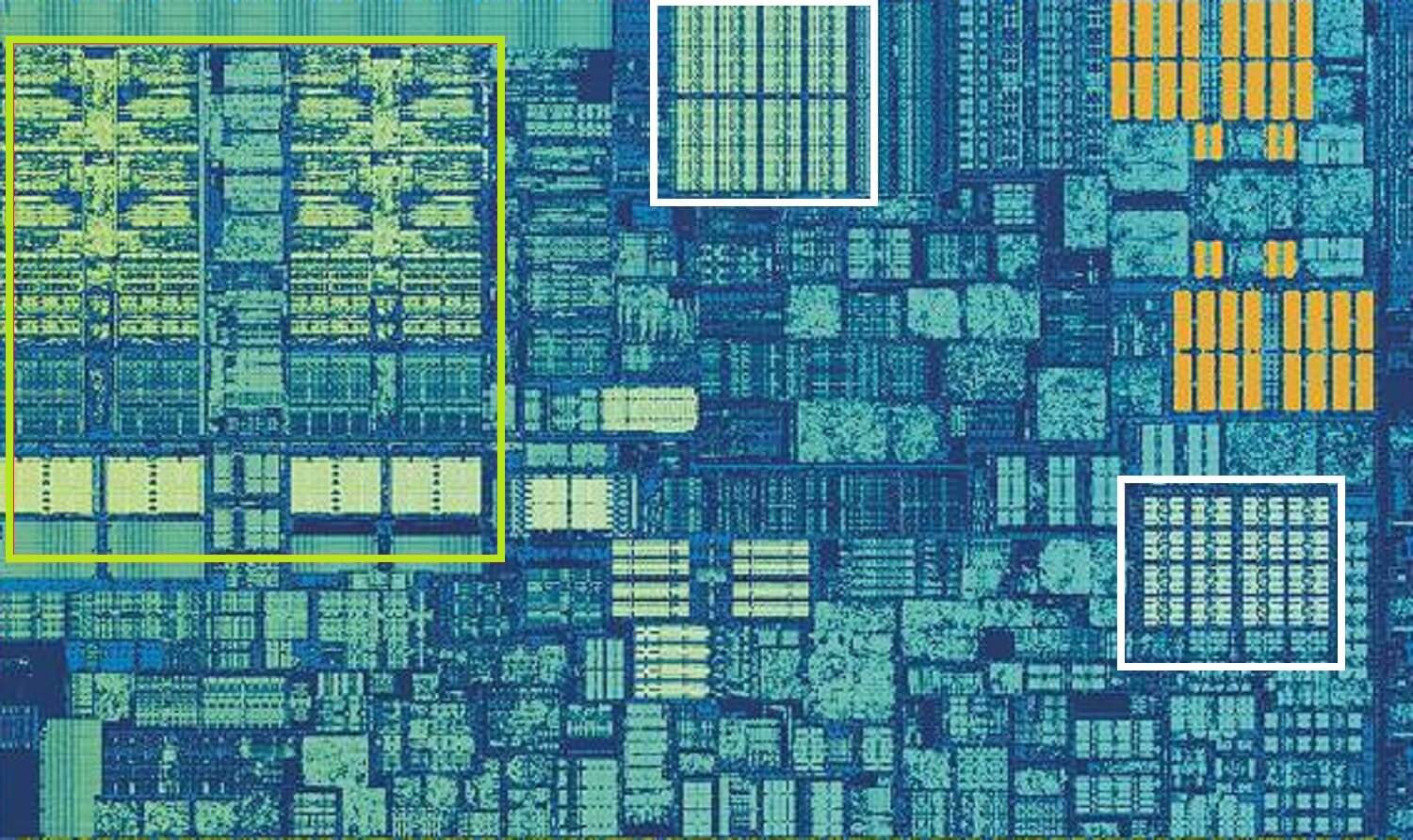

Intel Skylake CPU, ampliada na imagem de um único núcleo. Fonte: Wikichip

A imagem acima é uma imagem ampliada de um único núcleo do projeto de processador Skylake da Intel.

os ficheiros ALUs e os ficheiros de Registo podem ser vistos na extrema esquerda, realçados em verde. No topo-meio da imagem, em branco, está o cache de dados de Nível 1. Isto não contém muita informação, apenas 32 kB, mas como registros, está muito perto das unidades lógicas e corre na mesma velocidade que eles.

o outro rectângulo branco indica a cache de Instruções de Nível 1, também com 32 kB de tamanho. Como seu nome sugere, isso armazena vários comandos prontos para serem divididos em pequenas, chamadas micro operações (geralmente rotuladas como µops), para que o ALUs execute. Há um cache para eles, também, e você poderia classificá-lo como Nível 0, uma vez que é menor (apenas mantendo 1.500 operações) e mais próximo do que os caches L1.você pode estar se perguntando Por que esses blocos de SRAM são tão pequenos; por que eles não são um megabyte em tamanho? Juntos, os caches de dados e instruções ocupam quase a mesma quantidade de espaço no chip como as principais unidades lógicas fazem, de modo que torná-los maiores iria aumentar o tamanho geral do dado.

mas a principal razão pela qual eles apenas possuem alguns kB, é que o tempo necessário para encontrar e recuperar dados aumenta à medida que a capacidade de memória fica maior. Cache L1 precisa ser muito rápido, e então um compromisso deve ser alcançado, entre o tamanho ea velocidade — na melhor das hipóteses, leva cerca de 5 ciclos de relógio (mais longo para valores de ponto flutuante) para obter os dados deste cache, pronto para uso.

cache L2 de Skylake: 256 kB of SRAM goodness

mas se este fosse o único cache dentro de um processador, então seu desempenho iria bater uma parede súbita. É por isso que todos eles têm um outro nível de memória construído nos núcleos: o cache de Nível 2. Este é um bloco geral de armazenamento, segurando as instruções e dados.

é sempre um pouco maior do que o Nível 1: AMD Zen 2 processadores empacotam até 512 kB, de modo que o nível mais baixo caches pode ser mantido bem fornecido. Este tamanho extra vem a um custo, no entanto, e leva aproximadamente o dobro do tempo para encontrar e transferir os dados deste cache, em comparação com o Nível 1.

indo para trás no tempo, para os dias do Intel Pentium original, cache Nível 2 era um chip separado, ou em uma pequena placa de circuito plug-in (como um DIMM RAM) ou construído na placa-mãe principal. Ele eventualmente trabalhou seu caminho para o pacote CPU em si, até ser finalmente integrado no die CPU,nos processadores Pentium III e AMD K6-III.

Este desenvolvimento foi logo seguido por outro nível de cache, lá para suportar os outros níveis mais baixos, e veio devido ao aumento de chips multi-core.

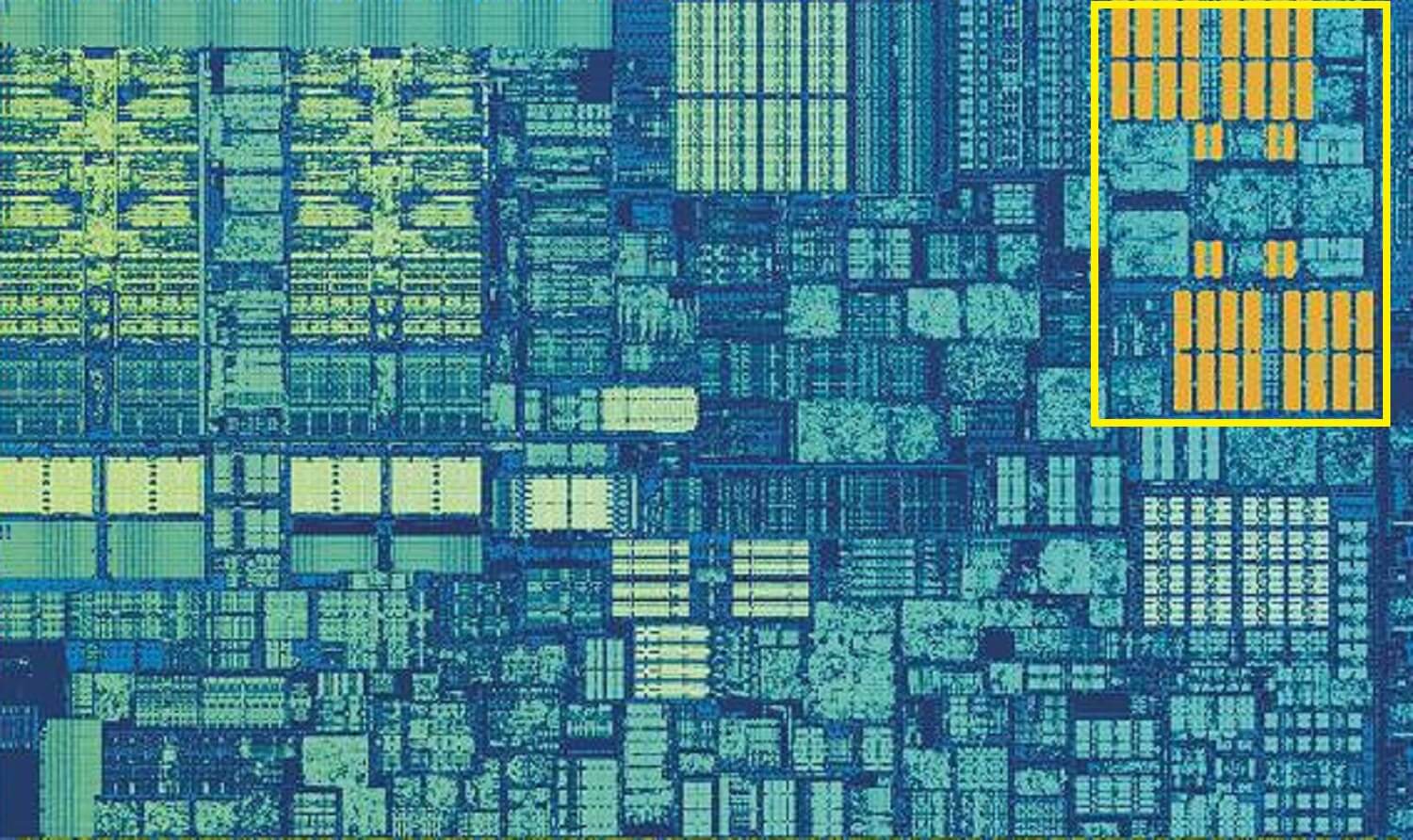

Intel Kaby Lake chip. Fonte: Wikichip

esta imagem, de um chip Intel Kaby Lake, mostra 4 núcleos no meio esquerdo (uma GPU integrada ocupa quase metade do die, à direita). Cada núcleo tem seu próprio conjunto “privado” de baratas de Nível 1 e 2 (destaques brancos e amarelos), mas eles também vêm com um terceiro conjunto de blocos de SRAM.

cache de Nível 3, mesmo que seja diretamente em torno de um único núcleo, é totalmente compartilhado com os outros — cada um pode acessar livremente o conteúdo do cache L3 de outro. É muito maior (entre 2 e 32 MB), mas também muito mais lento, com média de 30 ciclos, especialmente se um núcleo precisa usar dados que estão em um bloco de cache a alguma distância.

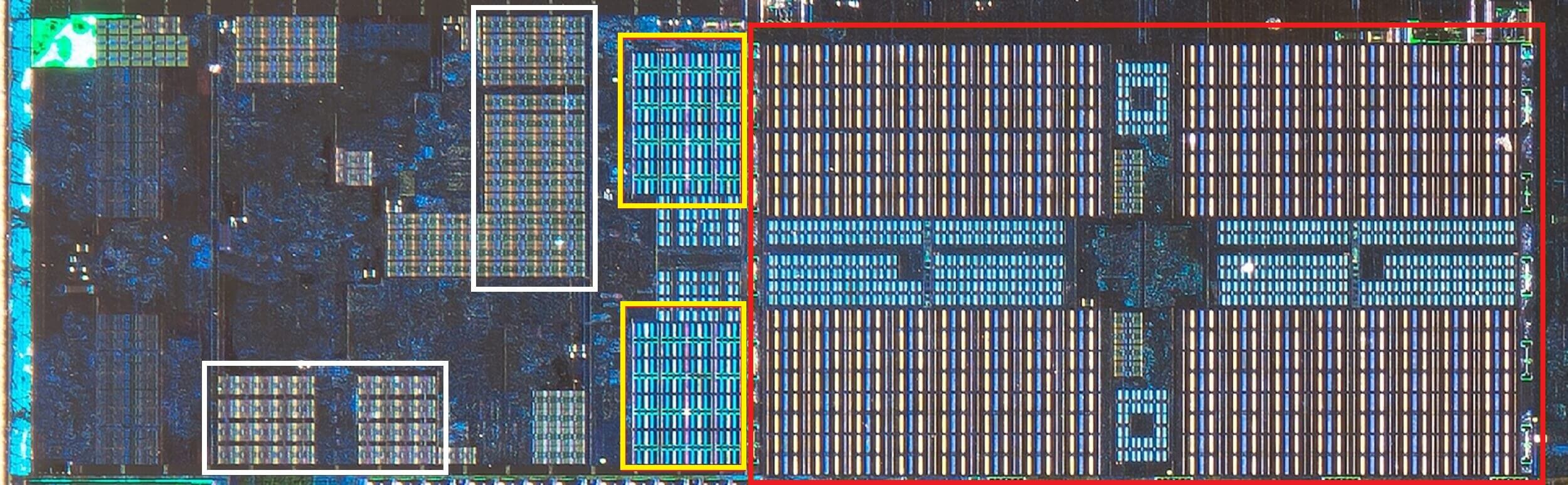

abaixo, podemos ver um único núcleo na arquitetura Zen 2 da AMD: os dados de Nível 1 de 32 kB e caches de instrução em branco, o nível 2 de 512 KB em amarelo, e um enorme bloco de 4 MB de cache L3 em vermelho.

AMD Zen 2 CPU, zoomed in shot of a single core. Fonte: Fritzchens Fritz

espere um segundo. Como podem 32 kB ocupar mais espaço físico do que 512 kB? Se o Nível 1 contém tão poucos dados, por que é proporcionalmente muito maior que o cache L2 ou L3?

mais do que apenas um número

Cache aumenta o desempenho acelerando a transferência de dados para as unidades lógicas e mantendo uma cópia de instruções e dados frequentemente usados nas proximidades. A informação armazenada em cache é dividida em duas partes: os dados em si e a localização de onde foi originalmente localizado na memória/armazenamento do sistema — Este endereço é chamado de tag de cache.

Quando a CPU executa uma operação que quer ler ou escrever dados de/para a memória, ela começa por verificar as tags na cache de Nível 1. Se o necessário está presente (um acerto de cache), que os dados podem então ser acessados quase imediatamente. Uma falha de cache ocorre quando a tag necessária não está no nível mais baixo de cache.

assim, uma nova tag é criada no cache L1, e o resto da arquitetura do processador assume, caçando de volta através dos outros níveis de cache (todo o caminho de volta para a unidade de armazenamento principal, se necessário) para encontrar os dados para essa tag. Mas para criar espaço no cache L1 para esta nova tag, algo mais invariavelmente tem que ser inicializado para o L2.

isso resulta em um shuffling quase constante sobre os dados, todos alcançados em apenas um punhado de ciclos de clock. A única maneira de conseguir isso é Tendo uma estrutura complexa em torno do SRAM, para lidar com a gestão dos dados. Por outras palavras:: se um núcleo de CPU consistia de apenas um JANTES, então o cache L1 seria muito mais simples, mas uma vez que existem dezenas deles (muitos dos quais será malabarismo com duas linhas de instruções), o cache requer múltiplas conexões para manter tudo em movimento.

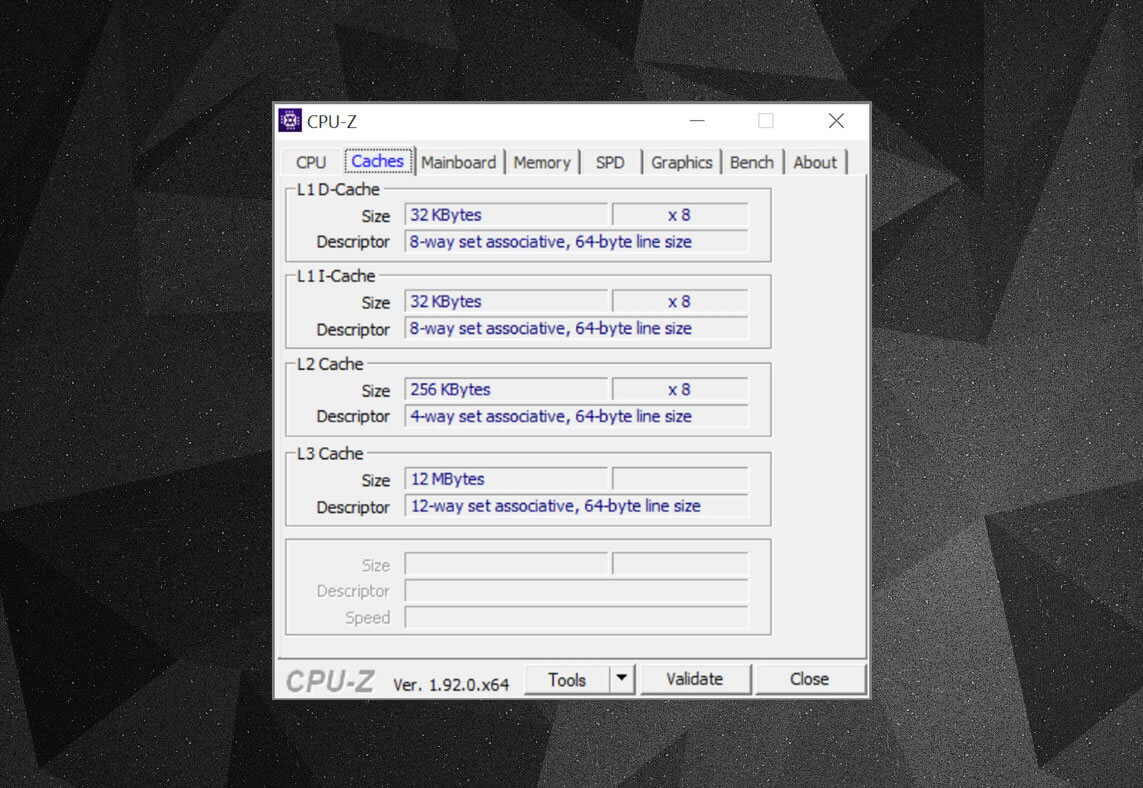

Você pode usar programas livres, como CPU-Z, para verificar a informação de cache para o processador alimentando seu próprio computador. Mas o que significa toda essa informação? Um elemento importante é o conjunto de etiquetas associativo — isto é tudo sobre as regras impostas pela forma como blocos de dados da memória do sistema são copiados para o cache.

a informação de cache acima é para um núcleo Intel i7-9700K.os seus caches de Nível 1 são cada um dividido em 64 blocos pequenos, chamados conjuntos, e cada um destes é ainda dividido em linhas de cache (64 bytes em tamanho). Set associative significa que um bloco de dados da memória do sistema é mapeado para as linhas de cache em um determinado conjunto, ao invés de ser livre para mapear em qualquer lugar.

a parte 8-way nos diz que um bloco pode ser associado com 8 linhas de cache em um conjunto. Quanto maior o nível de associatividade (ou seja, mais ‘maneiras’), maiores as chances de obter um cache atingido quando a CPU vai à caça de dados, e uma redução nas penalidades causadas por falhas de cache. As desvantagens são que ele adiciona mais complexidade, maior consumo de energia, e também pode diminuir o desempenho, porque há mais linhas de cache para processar para um bloco de dados.

L1+L2 cache inclusivo, cache de vítimas L3, Políticas de escrita, até ECC. Fonte: Fritzchens Fritz

outro aspecto da complexidade do cache gira em torno de como os dados são mantidos nos vários níveis. As regras são estabelecidas em algo chamado de política de inclusão. Por exemplo, processadores Intel Core têm cache L1+L3 totalmente inclusivo. Isto significa que os mesmos dados no nível 1, por exemplo, também podem estar no nível 3. Isto pode parecer que está desperdiçando valioso espaço de cache, mas a vantagem é que se o processador tem uma falha, ao procurar por uma tag em um nível inferior, ele não precisa caçar através do nível superior para encontrá-lo.

nos mesmos processadores, o cache L2 não é inclusivo: todos os dados armazenados lá não são copiados para qualquer outro nível. Isso economiza espaço, mas resulta que o sistema de memória do chip tem que pesquisar através de L3 (que é sempre muito maior) para encontrar uma tag perdida. Caches de vítimas são semelhantes a isso, mas eles são usados para armazenar informações que são empurradas para fora de um nível mais baixo — por exemplo, processadores Zen 2 da AMD usam cache de vítimas L3 que apenas armazena dados de L2.

existem outras políticas para cache, como quando os dados são escritos em cache e a memória principal do sistema. Estes são chamados de políticas de escrita e a maioria dos CPUs de hoje usam caches de write-back; isso significa que quando os dados são escritos em um nível de cache, há um atraso antes que a memória do sistema seja atualizada com uma cópia dele. Na maioria das vezes, esta pausa é executada enquanto os dados permanecerem no cache — só uma vez que ele é inicializado, a RAM obtém a informação.

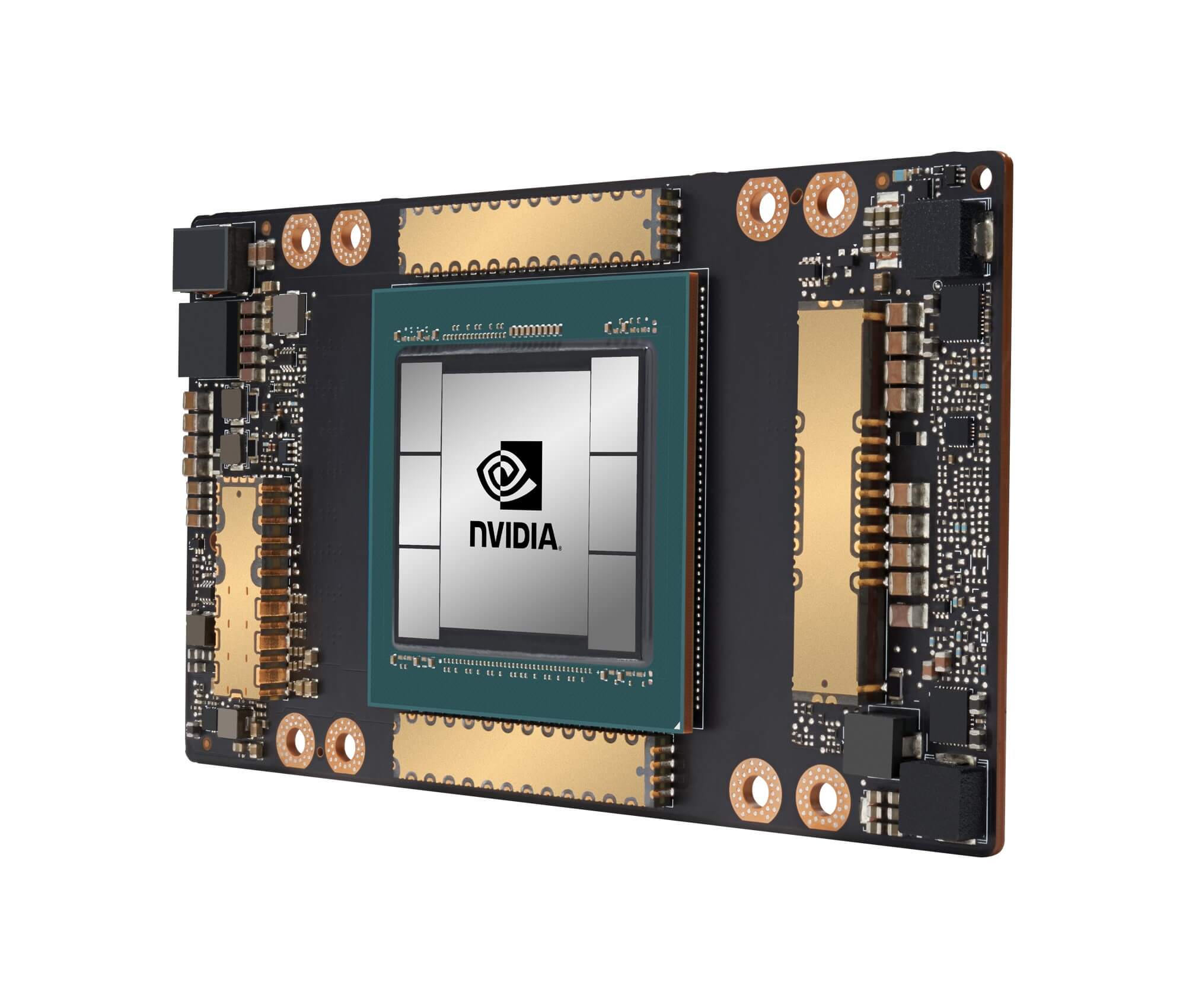

Nvidia GA100 processador de gráficos, embalado com um total de 20 MB de L1 e 40 MB de cache L2

Para o processador designers, escolhendo a quantidade, o tipo e a política de cache é tudo sobre o balanço entre o desejo de uma maior capacidade do processador contra o aumento da complexidade e necessário morrer espaço. Se fosse possível ter caches de Nível 1 associativo de 20 MB, 1000-way totalmente associativo sem que os chips se tornassem do tamanho de Manhattan (e consumindo o mesmo tipo de poder), então todos nós teríamos computadores com tais chips!

O nível mais baixo de caches nos CPUs de hoje não mudou muito na última década. No entanto, o cache de Nível 3 continuou a crescer em tamanho. Há uma década, conseguias 12 MB, se tivesses a sorte de ter uma informação de 999 i7-980X.Cache

, em poucas palavras: absolutamente necessário, peças absolutamente incríveis de tecnologia. Nós não olhamos para outros tipos de caches em CPUs e GPUs (como buffers de pesquisa de tradução ou caches de textura), mas uma vez que todos eles seguem uma estrutura simples e padrão de níveis como temos coberto aqui, eles talvez não soem tão complicados.você possuía um computador que tinha cache L2 na placa-mãe? Que tal aqueles CPUs de Pentium II e Celeron baseados em slot machines (por exemplo, 300a) que vieram numa daughterboard? Lembras-te da tua primeira CPU que partilhou L3? Deixe-nos saber na seção de comentários.atalhos de compras:

- AMD Ryzen 9 3900X na Amazon

- AMD Ryzen 9 3950X na Amazon

- Intel Core i9-10900K na Amazon

- AMD Ryzen 7 3700X na Amazon

- Intel Core i7-10700K na Amazon

- AMD Ryzen 5 3600 na Amazon

- Intel Core i5-10600K na Amazon

continue Lendo. Explainers at TechSpot

- Wi-Fi 6 Explained: the Next Generation of Wi-Fi

- What Are Tensor Cores?o que é o Chip Binning?

Leave a Reply